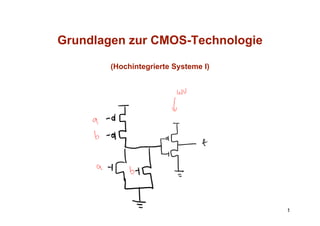

Das Dokument behandelt die Grundlagen der CMOS-Technologie, einschließlich der Vorteile wie niedrige Leistungsaufnahme, hohe Geschwindigkeit und Skalierbarkeit. Es erklärt die Funktionsweise von MOS-Transistoren, die verschiedenen Typen (n- und p-Kanal), ihre Stromgleichungen sowie die Schaltereigenschaften und das Layout von CMOS-Invertern. Zudem werden komplexe Gatterstrukturen und deren Eigenschaften sowie die Bedeutung von Designüberlegungen erläutert.