Deld lab manual

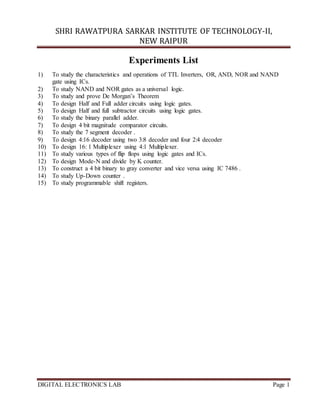

- 1. DIGITAL ELECTRONICS LAB Page 1 SHRI RAWATPURA SARKAR INSTITUTE OF TECHNOLOGY-II, NEW RAIPUR Experiments List 1) To study the characteristics and operations of TTL Inverters, OR, AND, NOR and NAND gate using ICs. 2) To study NAND and NOR gates as a universal logic. 3) To study and prove De Morgan’s Theorem 4) To design Half and Full adder circuits using logic gates. 5) To design Half and full subtractor circuits using logic gates. 6) To study the binary parallel adder. 7) To design 4 bit magnitude comparator circuits. 8) To study the 7 segment decoder . 9) To design 4:16 decoder using two 3:8 decoder and four 2:4 decoder 10) To design 16: 1 Multiplexer using 4:1 Multiplexer. 11) To study various types of flip flops using logic gates and ICs. 12) To design Mode-N and divide by K counter. 13) To construct a 4 bit binary to gray converter and vice versa using IC 7486 . 14) To study Up-Down counter . 15) To study programmable shift registers.

- 2. DIGITAL ELECTRONICS LAB Page 2 EXPERIMENT – 1 Aim: To study the characteristics and operations of TTL Inverters, OR, AND, NOR and NAND gate using ICs. Apparatus: Bread board, wires, IC-7402(AND),7432(OR),7404 (NOT) Theory: 1. AND: Logical AND operation is defined as “the output is 1 if all the inputs are 1” Circuit of logical AND is shown below. It has N inputs (N>=2) and one output. Digital signals are applied at the input terminal marked A,B,C….,N, the other terminalbeing grounded(not shown in diagram). The output is obtained at the terminal marked Y,and it is also a digital signal. Mathematically, AND operation is written as Y=A AND B AND C Y=A .B. C Symbolic Diagram Truth Table A B Y=A.B INPUTS OUTPUT A B Y 0 0 0 0 1 0 1 0 0 1 1 1

- 3. DIGITAL ELECTRONICS LAB Page 3 2. OR: Logical OR operation is defined as “the output is 1 if at least one of the inputs is 1”.Circuit of logical OR is shown below. It has N inputs (N>=2) and one output. Digital signals are applied at the input terminal marked A, B, C….,N, the other terminal being grounded(not shown in diagram).The output is obtained at the terminal marked Y, and it is also a digital signal. Mathematically, OR operation is written asY=A OR B OR C Y=A +B+C+……+N Truth Table for OR GATE INPUTS OUTPUT A B Y 0 0 0 0 1 1 1 0 1 1 1 1

- 4. DIGITAL ELECTRONICS LAB Page 4 3.NOT: Logical NOT operation is also called as Inverter. It has one input (A) and one output(Y).Its logic Equation is written asY = NOT A And is read as “Y equals not A” or “Y equals complement of A”. Truth Table for NOT GATE i/p o/p A Y Mathematically, NOT operation is written as 0 1 Y= A’ 1 0

- 5. DIGITAL ELECTRONICS LAB Page 5 4. NAND Gate: The output is 1 when either of inputs A or B is 1, or if neither is 1. In otherwords, it is normally 1, going 0 only if both A and B are 1. Truth Table for NAND GATE Mathematically, INPUTS OUTPUT NAND operation is written as Y=(AB)’ A B Y 0 0 1 0 1 1 1 0 1 1 1 0

- 6. DIGITAL ELECTRONICS LAB Page 6 5. NOR Gate: A HIGH output (1) results if both the inputs to the gate are LOW (0). If one orboth input isHIGH (1) or LOW output (0) results. NOR is the result of the negation ofthe OR operator. NOR is a functionally complete operation -- combinations of NOR gatescan be combined to generate any other logical function. By contrast, the OR operator ismonotonic as it can only change LOW to HIGH but not vice versa. Truth Table for NOR GATE Mathematically, INPUTS OUTPUT NOR operation is written as Y=(A+B)’ A B Y 0 0 1 0 1 0 1 0 0 1 1 0 Result: All truth tables are verified for logic gates.

- 7. DIGITAL ELECTRONICS LAB Page 7 EXPERIMENT – 2 Aim: To study NAND and NORgates as a universal logic. Apparatus: IC 7402, IC 7400, Power supply, Connecting wires, Multimeter, Breadboard etc. Theory: Standard Procedures:- Analyzing the Problem:- NAND GATE: 1) NAND is the contraction of AND – NOT gates. 2) It has two or more inputs and only one output i.e. Y = A · B. 3) When all the inputs are HIGH, the output is LOW. If any one or both the inputs are LOW, then the output is HIGH. 4) The Logic symbol and the truth table of NAND gate is as shown here. 5) The small circle (or bubble) represents the operation of inversion. The NAND gate is equivalent to an OR gate with the bubble at its inputs which are as shown.

- 8. DIGITAL ELECTRONICS LAB Page 8 NOR GATE: 1) NOR is the contraction of OR – NOT gates. 2) It has two or more inputs and only one output i.e. Y = A + B. 3) When all the inputs are LOW, the output is HIGH. If any one or both the inputs are HIGH, then the output is LOW. 4) The Logic symbol and the truth table of NOR gate is as shown here. 5) The small circle (or bubble) represents the operation of inversion. The NOR gate is equivalent to an AND gate with the bubble at its inputs which are as shown

- 9. DIGITAL ELECTRONICS LAB Page 9 A universal gate is a gate which can implement any Boolean function without need to use any other gate type. The NAND and NOR gates are universal gates. In practice, this is advantageous since NAND and NOR gates are economical and easier to fabricate and are the basic gates used in all IC digital logic families. Designing the Solution: NAND GATE AS A UNIVERSAL GATE : To prove that any Boolean function can be implemented using only NAND gates, we will show that the AND, OR, and NOT operations can be performed using only these gates. IMPLEMENTING INVERTER USING NAND GATE : The figure shows two ways in which a NAND gate can be used as an inverter (NOT gate). All NAND input pins connect to the input signal A gives an output A’. One NAND input pin is connected to the input signal A while all other input pins are connected to logic 1. The output will be A’. IMPLEMENTING AND USING NAND GATE : An AND gate can be replaced by NAND gates as shown in the figure (The AND is replaced by a NAND gate with its output complemented by a NAND gate inverter).

- 10. DIGITAL ELECTRONICS LAB Page 10 IMPLEMENTING OR USING NAND GATE: An OR gate can be replaced by NAND gates as shown in the figure (The OR gate is replaced by a NAND gate with all its inputs complemented by NAND gate inverters). NOR GATE AS A UNIVERSAL GATE: To prove that any Boolean function can be implemented using only NOR gates, we will show that the AND, OR, and NOT operations can be performed using only these gates. IMPLEMENTING INVERTER USING NOR GATE: The figure shows two ways in which a NOR gate can be used as an inverter (NOT gate). All NOR input pins connect to the input signal A gives an output A’. One NOR input pin is connected to the input signal A while all other input pins are connected to logic 0. The output will be A’.

- 11. DIGITAL ELECTRONICS LAB Page 11 IMPLEMENTING OR USING NOR GATE : An OR gate can be replaced by NOR gates as shown in the figure (The OR is replaced by a NOR gate with its output complemented by a NOR gate inverter). IMPLEMENTING AND USING NOR GATE : An AND gate can be replaced by NOR gates as shown in the figure (The AND gate is replaced by a NOR gate with all its inputs complemented by NOR gate inverters). Basic IC needed are NAND gate and NOR gate. IC diagram are given as below Fig – Pin Diagram of NAND & NOR GATES

- 12. DIGITAL ELECTRONICS LAB Page 12 Implementing the Solution:- Plug the chips you will be using into the breadboard. Point all the chips in the same direction with pin 1 at the upper-left corner. (Pin 1 is often identified by a dot or a notch next to it on the chip package). Connect +5V and GND pins of each chip to the power and ground bus strips on the breadboard. Make the connections as per the circuit diagram. Switch on VCC and apply various combinations of input according to truth table. Note down the output readings for half/full adder and sum and the carry bit for different combinations of inputs in following Tables where S & V indicating logic value of the output. And fill your result in S (V) and C (V) in voltage. Where 5V indicating logic 1 and 0V indicating logic 0. · Testing the Solution:- · Truth Tables: · · · · · · · · · · · NAND Gate NOR Gate Inverter using Nand Gate And Using Nand Gate Or Using Nand Gate

- 13. DIGITAL ELECTRONICS LAB Page 13 Inverter Using Nor Gate Or Using Nor Gate And Using or Gate Conclusion:- A universal gate is a gate which can implement any Boolean function without need to use any other gate type. The NAND and NOR gates are universal gates.

- 14. DIGITAL ELECTRONICS LAB Page 14 EXPERIMENT – 3 Aim: To study and prove Demorgan’sTheorem. Apparatus: AND Gate (IC-7408),OR Gate (IC-7432),NOT Gate (IC-7404), Digital IC TrainerKIT,LED,Breadboard,Connecting wires. Theory: 1)De-Morgan’s first theorem states that 'the complement of a sum is equal to the product of Complements'. Bar (A+B) = Bar (A.B) NOR gate = Bubbled AND gate 2)De-Morgan's second theorem states that 'the complement of a product is equal to the sum of the complements'. Bar (A.B) = Bar (A+B) NAND gate = Bubbled OR gate

- 15. DIGITAL ELECTRONICS LAB Page 15 Truth table for theorem-1: A B LHS=Bar(A.B) RHS=Bar(A+B) 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0 0 Truth table for theorem-2: A B LHS=Bar(A+B) RHS=Bar(A.B) 0 0 1 1 0 1 0 0 1 0 0 0 1 1 0 0 Circuit diagram for theorem-1: Circuit diagram for theorem-2:

- 16. DIGITAL ELECTRONICS LAB Page 16 Procedure: 1) Take Digital Trainer KIT including Breadboard, ICs and connecting leads. 2) Insert ICs on the Breadboard. 3) According to pin configuration of IC perform the connections. 4) Connect VCC (+5V) to pin no.14 and Connect Pin no. 7 to GND of IC. 5) Apply different input and observe output at LED. 6) Verify the output according truth-table. Result: All the output verified the result of Truth Table and hence de-Morgan’s theorem is verified.

- 17. DIGITAL ELECTRONICS LAB Page 17 EXPERIMENT – 4 Aim: To design Half and Full adder circuits using logic gates. Apparatus: Bread board, wires, IC-7402(AND), 7432(OR), 7486 (XOR) Theory: Half Adder: Half Adder is a combinational circuit that performs addition of two bits. It has two inputs and two outputs. The two I/Ps are the two 1-bit numbers A and B designated as augend and addend bits. The two O/Ps are the sum ‘S’ of A and B and the carry bit, denoted by ‘C’. Truth Table of a half adder can be derived by performing binary addition of augend andaddend bits as follows: Truth Table for HALF-ADDER A B SUM CARRY From the truth table, Boolean Expression can be 0 0 0 0 derived as: 0 1 1 0 S = A’B + AB’ = A ⊕B 1 0 1 0 C = AB 1 1 0 1 A Half Adder circuit can be implemented using AND & OR logic gates or by using XOR & AND logic gates. Both these implementations are shown in the image below:

- 18. DIGITAL ELECTRONICS LAB Page 18 Since NAND is considered as Universal Logic Gate which means that all other logic gates can be derived from it, below is the implementation of a Half Adder circuit using NAND logic gate: Full Adder:- Full Adder is a combinational circuit that performs addition of three bits. It consists of three inputs and two outputs. Two of the inputs denoted by A and B are augends and addend bits that are to be added, & third input denoted by Cin presents the carry bit from the previous lower significant position. The two O/Ps are the sum ‘S’ of A and Band the carry bit, denoted by Co. A full adder circuit can be realized using half adder circuits as shown in the image below:

- 19. DIGITAL ELECTRONICS LAB Page 19 Using OR, XOR and AND logic gates, a full adder circuit can be implemented as below: Procedure: - 1) To pin number 14 of all IC’s Vccis applied & pin number 7 is grounded. 2) Assemble the circuit on breadboard according to the pin configuration. 3) Give the logical inputs and check for the proper output. Conclusion: Verified the truth table for half adder and full adder

- 20. DIGITAL ELECTRONICS LAB Page 20 EXPERIMENT – 5 Aim: To design Half and full subtractor circuits using logic gates. Apparatus: IC 7400, IC 7408, IC 7486, IC 7432, Patch Cords & IC Trainer Kit. Theory: Half Subtractor: Subtracting a single-bit binary value B from another A (i.e. A -B ) produces a difference bit D and a borrow out bit B-out. This operation is called half subtraction and the circuit to realize it is called a half subtractor. The Boolean functions describing the half- Subtractor are: Truth Table for HALF-SUBTRACTOR INPUTS OUTPUTS A B D Br 0 0 0 0 0 1 1 1 1 0 1 0 1 1 0 0 Boolean expressions for half-subtractor are, D = A⊕B Br = A’B

- 21. DIGITAL ELECTRONICS LAB Page 21 Full Subtractor: Subtracting two single-bit binary values, B, Cin from a single-bit value A produces a difference bit D and a borrow out Br bit. This is called full subtraction. TheBoolean functions describing the full-subtractor are: D = (x ⊕ y) ⊕ Cin⊕Br= A’B + A’(Cin) + B(Cin) A B Cin D Br 0 0 0 0 0 0 0 1 1 1 0 1 0 1 1 0 1 1 0 1 1 0 0 1 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1

- 22. DIGITAL ELECTRONICS LAB Page 22 Procedure: 1. Check the components for their working. Insert the appropriate IC into the IC base. 2. Make connections as shown in the circuit diagram. 3. Verify the Truth Table and observe the outputs. Result: The truth table of the above circuits is verified.

- 23. DIGITAL ELECTRONICS LAB Page 23 EXPERIMENT – 6 Aim: To study the binary parallel adder. Apparatus: IC 7483, IC 7486, Patch Cords & IC Trainer Kit. Theory: The Full adder can add single-digit binary numbers and carries. The largest sum that can be obtained using a full adder is 112. Parallel adders can add multiple-digit numbers. If fulladders are placed in parallel, we can add two- or four-digit numbers or any other size desired. Figure below uses STANDARD SYMBOLS to show a parallel adder capable of adding two, two-digit binary numbers The addend would be on A inputs, and the augend on the B inputs. For this explanation we will assume there is no input to C0 (carry from a previous circuit) To add 102 (addend) and 012 (augend), the addend inputs will be 1 on A2 and 0 on A1. The augend inputs will be 0 on B2 and 1 on B1. Working from right to left, as we do in normal addition, let’s calculate the outputs of each full adder. With A1 at 0 and B1 at 1, the output of adder1 will be a sum (S1) of 1 with no carry (C1). Since A2 is 1 and B2 is 0, we have a sum (S2) of 1 with no carry (C2) from adder1. To determine the sum, read the outputs (C2, S2, and S1) from left to right. In this case, C2 = 0, S2 = 1, and S1 = 1. The sum, then, of 102 and 012 is 0112. To add four bits we require four full adders arranged in parallel. IC 7483 is a 4- bit parallel adder whose pin diagram is shown.

- 24. DIGITAL ELECTRONICS LAB Page 24 i) 4-Bit Binary Adder An Example: 7+2=11 (1001) 7 is realized at A3 A2 A1 A0 = 0111 2 is realized at B3 B2 B1 B0 = 0010 Sum = 1001 ADDERCIRCUIT:

- 25. DIGITAL ELECTRONICS LAB Page 25 Procedure: Check all the components for their working. Insert the appropriate IC into the IC base. Make connections as shown in the circuit diagram. Apply augend and addend bits on A and B and Cin=0. Verify the results and observe the outputs Result:Verified the working of IC 7483 as Binary parallel adder.

- 26. DIGITAL ELECTRONICS LAB Page 26 EXPERIMENT – 7 Aim: To design 4 bit magnitude comparator circuits. Apparatus: IC 7486, IC 7432, IC 7408, IC 7400, Power supply, Connecting wires, Multimeter. Theory: Analyzing the Problem:- The comparison of two numbers is an operator that determines one number is greater than, less than (or) equal to the other number. A magnitude comparator is a combinational circuit that compares two numbers A and B and determines their relative magnitude. The outcome of the comparator is specified by three binary variables that indicate whether A>B, A=B (or) A<B. A = A3 A2 A1 A0 B = B3 B2 B1 B0 The equality of the two numbers and B is displayed in a combinational circuit designated by the symbol (A=B). This indicates A greater than B, then inspect the relative magnitude of pairs of significant digits starting from most significant position. A is 0 and that of B is 0. We have A<B, the sequential comparison can be expanded as The same circuit can be used to compare the relative magnitude of two BCD digits. Where, A = B is expanded as,

- 27. DIGITAL ELECTRONICS LAB Page 27 Designing the Solution:- 4 BIT MAGNITUDE COMPARATOR Pin Configuration of 7485: Pin Diagram & Logic Diagram: Fig - Pin Diagram & Logic Diagram of IC 7485

- 28. DIGITAL ELECTRONICS LAB Page 28 Procedure: Plug the chips you will be using into the breadboard. Point all the chips in the same direction with pin 1 at the upper-left corner. (Pin 1 is often identified by a dot or a notch next to it on the chip package). Connect +5V and GND pins of each chip to the power and ground bus strips on the breadboard. Make the connections as per the circuit diagram. Switch on VCC and apply various combinations of input according to truth table. Take 2 4bit nos& Write output in observation table. Result: 4-bit Magnitude comparator circuit is designed.

- 29. DIGITAL ELECTRONICS LAB Page 29 EXPERIMENT – 8 Aim: To study the 7 segment decoder . Apparatus: IC7447, 7-Segment display (common anode), Patch chords, resistor (1K_) & IC Trainer Kit Theory: The Light Emitting Diode (LED) finds its place in many applications in these modernelectronic fields. One of them is the Seven Segment Display. Seven-segment displayscontains the arrangement of the LEDs in “Eight” (8) passion, and a Dot (.) with a commonelectrode, lead (Anode or Cathode). The purpose of arranging it in that passion is that we canmake any number out of that by switching ON and OFF the particular LED's. Here is theblock diagram of the Seven Segment LED arrangement. LED’s are basically of two types- 1)Common Cathode (CC) -All the 8 anode legs uses only one cathode, which is common. 2)Common Anode (CA)-The common leg for all the cathode is of Anode type. A decoder is a combinational circuit that connects the binary information from ‘n’ input lines to a maximum of 2n unique output lines. The IC7447 is a BCD to 7-segment patternconverter. The IC7447 takes the Binary Coded Decimal (BCD) as the input and outputs the relevant 7 segment code.

- 30. DIGITAL ELECTRONICS LAB Page 30 CIRCUIT DIAGRAM: TRUTH TABLE: Procedure Check all the components for their working. Insert the appropriate IC into the IC base. Make connections as shown in the circuit diagram. Verify the Truth Table and observe the outputs. Result: 7-Segment Decoder is studied and designed.

- 31. DIGITAL ELECTRONICS LAB Page 31 EXPERIMENT – 9 Aim: To study various types of flip flops using logic gates and ICs. Apparatus: Power supply, Digital Trainer kit, ICs – 7474, Connecting wires, Multimeter,CRO,PulseGenerator, Patch Chords, IC 7400 NAND gate IC, IC 7402 NOR gate IC, IC 7404 NOT gate IC, LED. Theory: Analyzing the Problem:- FLIP-FLOP:- "Flip-flop" is the common name given to two-state devices which offer basic memory for sequential logic operations. Flip-flops are heavily used for digital data storage and transfer and are commonly used in banks called "register" for the storage of binary numerical data. D-Type flip-flop (Toggle switch) : The operations of a D flip-flop are much more simpler. It has only one input addition to the clock. It is very useful when a single data bit (0 or 1) is to bestored. If there is a HIGH on the D input when a clock pulse is applied, the flip-flop SETs and stores a 1. If there is a LOW on the D input when a clock pulse is applied, the flip-flop RESETs and stores a0. To implement D flip-flop we require NAND gates and NOR gates. The truth table for D flip flop is shown below: i/p o/p Q D Q(t+1) 0 0 0 0 1 1 1 0 0 1 1 1

- 32. DIGITAL ELECTRONICS LAB Page 32 J-K flip-flop: The J-K flip-flop works very similar to S-R flip-flop. The only difference is that this flip-flop has NO invalid state. The truth table is shown below. T flip-flop: This type of flip-flop is a simplified version of the JK flip-flop. It is not usually found as an IC chip by itself, but is used in many kinds of circuits, especially counter and dividers. Its only function is that it toggles itself with every clock pulse (on either the leading edge, on the trailing edge) it can be constructed from the RS flip-flop. The truth table is shown below. i/p o/p Q J K Q(t+1) 0 0 0 0 0 0 1 0 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 0 1 1 0 1 1 1 1 0

- 33. DIGITAL ELECTRONICS LAB Page 33 Truth Table:- i/p o/p Q T Q(t+1) 0 0 0 0 - 1 1 0 1 1 - 0 Pin Diagrams of Basic gates ICs used in experiment:

- 34. DIGITAL ELECTRONICS LAB Page 34 Designing the Solution:- 2)JKFlipFlop 3)T-Flip-Flop Implementing the Solution:-

- 35. DIGITAL ELECTRONICS LAB Page 35 i) Flip-Flop: - The R –S Flip flop has two data inputs R & S. Generation of two signals to drive a flip flop is a disadvantage in much application. Furthermore, the forbidden condition of both R and S high may occur inadvertently. This has lid to the D Flip Flop a circuit that needs only a single data input. Fig shows the simple diagram of D Flip- Flop using NOR Gate. In this circuit the D input is just transferred to the output e.g. If D =0 then output Q isalso & If D = 1 output is also 1, as shown in the truth table. J-K Flip-flop:- JK Flip-Flop is the most versatile binary strange element. It can perform all the functions of SR and D flip-flop. The uncertainty in the State of SR Flip- Flop when S = R = 1 can be eliminated by using JK Flip-Flop. T Flip –Flop: - The basic digital memory circuit is known as flip flop. It two stable states which are known as the 1 state 0 state. It can be obtained by using NAND orNOR gates. Generally there are two inputs to the flip flops (R, S or J K) and two outputs Q and Q’. The outputs Q and Q’ are always complementary. The circuit has two stable state Q=1which is referred to as the1 state( or set state ) whereas in the other stable state Q’=0 which is referred to as the 0 sate ( or reset state ) . If the circuit is in 1 state. It continues to remain in this state and similarly if it is in 0 state, it continues to remain in this state. This property of the circuit is referred to as memory, that is it can store 1 bit of digital information. In a JK flip flop, if J=K the resulting flip flop is referred to as a T Flip Flop, as shown in fig. It has only input, referred to as T input. Its truth table is given in table 1. If T=1 it acts as a toggle switch for every clock pulse the output Q changes.

- 36. DIGITAL ELECTRONICS LAB Page 36 Procedure: - · Study the circuit diagram. · Connect the circuit as shown in fig i.e. JK Flip Flop by using connecting wires. · Switch ‘ON’ the power supply. · Apply proper I/P to J & K I/Ps of Flip-Flop from Logic I/P · Check the O/P on Logic O/P Section. · Change the I/P & Verify the Truth Table. Result: so using the ICs-7474 and gates we can study and verify the different flip flops like D, JK and T.

- 37. DIGITAL ELECTRONICS LAB Page 37 EXPERIMENT – 10 Aim: To construct a 4 bit binary to gray converter and vice versa using IC 7486 . Apparatus: IC 7486, Power supply, Connecting wires, Multimeter, BreadBoard, etc. Theory: Designing the Solution:- IC Diagram of XOR GATE:- BINARY TO GRAY CODE CONVERTOR:-

- 38. DIGITAL ELECTRONICS LAB Page 38 GRAY CODE TO BINARY CONVERTOR: Implementing the Solution:- Plug the chips you will be using into the breadboard. Point all the chips in the same direction with pin 1 at the upper-left corner. (Pin 1 is often identified by a dot or a notch next to it on the chip package). Connect +5V and GND pins of each chip to the power and ground bus strips on the breadboard. Make the connections as per the circuit diagram. Switch on VCC and apply various combinations of input according to truth table. In the case of binary to gray conversion, the inputs B0, B1, B2 and B3 are given at respective pins and outputs G0, G1, G2, G3 are taken for all the 16 combinations of the input. In the case of gray to binary conversion, the inputs G0, G1, G2 and G3 are given at respective pins and outputs B0, B1, B2, and B3 are taken for all the 16 combinations of inputs. The values of the outputs are tabulated. Results: We designed and simulated a Gray code converter that converts binary coded numbers to Gray coded numbers and vice versa.

- 39. DIGITAL ELECTRONICS LAB Page 39 EXPERIMENT – 11 Aim: To study Up-Down counter. Apparatus: IC 7476, Patch Cords & IC Trainer Kit Theory: A counter in which each flip-flop is triggered by the output goes to previous flip-flop.As all the flip-flops do not change state simultaneously spike occur at the output. To avoidthis, strobe pulse is required. Because of the propagation delay the operating speed ofasynchronous counter is low. Asynchronous counter are easy and simple to construct. MOD-8 UP COUNTER

- 40. DIGITAL ELECTRONICS LAB Page 40 Truth Table for MOD-8 up counter CLK QC QB QA 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 6 1 1 0 7 1 1 1 8 0 0 0 MOD-6 UP COUNTER CIRCUIT DIAGRAM:

- 41. DIGITAL ELECTRONICS LAB Page 41 Truth Table for MOD-6 up counter CLK QC QB QA 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 6 0 0 0 MOD-8 DOWN COUNTER CIRCUIT DIAGRAM:

- 42. DIGITAL ELECTRONICS LAB Page 42 Truth Table for MOD-8 down counter CLK QC QB QA 0 1 1 1 1 1 1 0 2 1 0 1 3 1 0 0 4 0 1 1 5 0 1 0 6 0 0 1 7 0 0 0 8 1 1 1 MOD-6 DOWN COUNTER CIRCUIT DIAGRAM:

- 43. DIGITAL ELECTRONICS LAB Page 43 Truth Table for MOD-6 down counter CLK QC QB QA 0 1 1 1 1 1 1 0 2 1 0 1 3 1 0 0 4 0 1 1 5 0 1 0 6 1 1 1 PROCEDURE: Check all the components for their working. Insert the appropriate IC into the IC base. Make connections as shown in the circuit diagram. Verify the Truth Table and observe the outputs. RESULT: The working of up-down counter is verified.

- 44. DIGITAL ELECTRONICS LAB Page 44 EXPERIMENT – 12 Aim: To study programmable shift registers Apparatus: IC 7495, Patch Cords & IC Trainer Kit. Theory: 1) SERIAL IN SERIAL OUT (SISO) (Right Shift) 2)Serial Shift QA QB QC QD i/p pulses data - - X X X X 0 t1 0 X X X 1 t2 1 0 X X 0 t3 0 1 0 X 1 t4 1 0 1 0 X t5 X 1 0 1 X t6 X X 1 0 X t7 X X X 1 X t8 X X X X 2) SERIAL IN PARALLEL OUT (SIPO) Serial Shift QA QB QC QD i/p pulses data - - X X X X 0 t1 0 X X X 1 t2 1 0 X X 0 t3 0 1 0 X 1 t4 1 0 1 0 3) PARALLEL IN PARALLEL OUT (PIPO) clock Shift QA QB QC QD i/p pulses terminal - - X X X X CLK2 t1 1 0 1 0

- 45. DIGITAL ELECTRONICS LAB Page 45 3) PARALLEL IN SERIAL OUT (PISO) clock i/p Shift QA QB QC QD terminal pulses - - X X X X CLK2 t1 1 0 1 0 CLK2 t2 X 1 0 1 0 t3 X X 1 0 1 t4 X X X 1 X t5 X X X X PROCEDURE: Check all the components for their working. Insert the appropriate IC into the IC base. Make connections as shown in the circuit diagram. Verify the Truth Table and observe the outputs . Result: The various operations of a programmable shift register is verified.