xilinx fpga problems

•

1 gefällt mir•3,166 views

Melden

Teilen

Melden

Teilen

Downloaden Sie, um offline zu lesen

Empfohlen

Weitere ähnliche Inhalte

Was ist angesagt?

Was ist angesagt? (20)

Andere mochten auch

Andere mochten auch (20)

Ähnlich wie xilinx fpga problems

Electrónica digitalElectrónica digital: Diseño de contador con flip-flop tipo JK y D haciendo de...

Electrónica digital: Diseño de contador con flip-flop tipo JK y D haciendo de...SANTIAGO PABLO ALBERTO

FSM, finite state machineLec16 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Fi...

Lec16 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Fi...Hsien-Hsin Sean Lee, Ph.D.

Ähnlich wie xilinx fpga problems (20)

Sequential Circuitsdddddddddddddddddsssssssssss-ppt.pptx

Sequential Circuitsdddddddddddddddddsssssssssss-ppt.pptx

Electrónica digital: Diseño de contador con flip-flop tipo JK y D haciendo de...

Electrónica digital: Diseño de contador con flip-flop tipo JK y D haciendo de...

Lec16 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Fi...

Lec16 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Fi...

CSCMPE 3430, sp16 – Assignment 5 (30 points total) Due S.docx

CSCMPE 3430, sp16 – Assignment 5 (30 points total) Due S.docx

Kürzlich hochgeladen

Call Girl Aurangabad Indira Call Now: 8617697112 Aurangabad Escorts Booking Contact Details WhatsApp Chat: +91-8617697112 Aurangabad Escort Service includes providing maximum physical satisfaction to their clients as well as engaging conversation that keeps your time enjoyable and entertaining. Plus they look fabulously elegant; making an impressionable. Independent Escorts Aurangabad understands the value of confidentiality and discretion - they will go the extra mile to meet your needs. Simply contact them via text messaging or through their online profiles; they'd be more than delighted to accommodate any request or arrange a romantic date or fun-filled night together. We provide –(INDIRA) Call Girl Aurangabad Call Now 8617697112 Aurangabad Escorts 24x7

(INDIRA) Call Girl Aurangabad Call Now 8617697112 Aurangabad Escorts 24x7Call Girls in Nagpur High Profile Call Girls

Booking open Available Pune Call Girls Pargaon 6297143586 Call Hot Indian Girls Waiting For You To Fuck

Booking Contact Details

WhatsApp Chat: +91-6297143586

pune Escort Service includes providing maximum physical satisfaction to their clients as well as engaging conversation that keeps your time enjoyable and entertaining. Plus they look fabulously elegant; making an impressionable.

Independent Escorts pune understands the value of confidentiality and discretion - they will go the extra mile to meet your needs. Simply contact them via text messaging or through their online profiles; they'd be more than delighted to accommodate any request or arrange a romantic date or fun-filled night together.

We provide -

01-may-2024(v.n)

Booking open Available Pune Call Girls Pargaon 6297143586 Call Hot Indian Gi...

Booking open Available Pune Call Girls Pargaon 6297143586 Call Hot Indian Gi...Call Girls in Nagpur High Profile

Model Call Girl Services in Delhi reach out to us at 🔝 9953056974 🔝✔️✔️

Our agency presents a selection of young, charming call girls available for bookings at Oyo Hotels. Experience high-class escort services at pocket-friendly rates, with our female escorts exuding both beauty and a delightful personality, ready to meet your desires. Whether it's Housewives, College girls, Russian girls, Muslim girls, or any other preference, we offer a diverse range of options to cater to your tastes.

We provide both in-call and out-call services for your convenience. Our in-call location in Delhi ensures cleanliness, hygiene, and 100% safety, while our out-call services offer doorstep delivery for added ease.

We value your time and money, hence we kindly request pic collectors, time-passers, and bargain hunters to refrain from contacting us.

Our services feature various packages at competitive rates:

One shot: ₹2000/in-call, ₹5000/out-call

Two shots with one girl: ₹3500/in-call, ₹6000/out-call

Body to body massage with sex: ₹3000/in-call

Full night for one person: ₹7000/in-call, ₹10000/out-call

Full night for more than 1 person: Contact us at 🔝 9953056974 🔝. for details

Operating 24/7, we serve various locations in Delhi, including Green Park, Lajpat Nagar, Saket, and Hauz Khas near metro stations.

For premium call girl services in Delhi 🔝 9953056974 🔝. Thank you for considering us!Call Now ≽ 9953056974 ≼🔝 Call Girls In New Ashok Nagar ≼🔝 Delhi door step de...

Call Now ≽ 9953056974 ≼🔝 Call Girls In New Ashok Nagar ≼🔝 Delhi door step de...9953056974 Low Rate Call Girls In Saket, Delhi NCR

Booking open Available Pune Call Girls Koregaon Park 6297143586 Call Hot Indian Girls Waiting For You To Fuck

Booking Contact Details

WhatsApp Chat: +91-6297143586

pune Escort Service includes providing maximum physical satisfaction to their clients as well as engaging conversation that keeps your time enjoyable and entertaining. Plus they look fabulously elegant; making an impressionable.

Independent Escorts pune understands the value of confidentiality and discretion - they will go the extra mile to meet your needs. Simply contact them via text messaging or through their online profiles; they'd be more than delighted to accommodate any request or arrange a romantic date or fun-filled night together.

We provide -

01-may-2024(v.n)

Booking open Available Pune Call Girls Koregaon Park 6297143586 Call Hot Ind...

Booking open Available Pune Call Girls Koregaon Park 6297143586 Call Hot Ind...Call Girls in Nagpur High Profile

Welcome to the April edition of WIPAC Monthly, the magazine brought to you by Water Industry Process Automation & Control.

In this month's edition, along with the latest news from the industry we have articles on:

The use of artificial intelligence and self-service platforms to improve water sustainability

A feature article on measuring wastewater spills

An article on the National Underground Asset Register

Have a good month,

OliverWater Industry Process Automation & Control Monthly - April 2024

Water Industry Process Automation & Control Monthly - April 2024Water Industry Process Automation & Control

Kürzlich hochgeladen (20)

Call Girls Walvekar Nagar Call Me 7737669865 Budget Friendly No Advance Booking

Call Girls Walvekar Nagar Call Me 7737669865 Budget Friendly No Advance Booking

Call Girls Pimpri Chinchwad Call Me 7737669865 Budget Friendly No Advance Boo...

Call Girls Pimpri Chinchwad Call Me 7737669865 Budget Friendly No Advance Boo...

Call for Papers - Educational Administration: Theory and Practice, E-ISSN: 21...

Call for Papers - Educational Administration: Theory and Practice, E-ISSN: 21...

CCS335 _ Neural Networks and Deep Learning Laboratory_Lab Complete Record

CCS335 _ Neural Networks and Deep Learning Laboratory_Lab Complete Record

Call Girls In Bangalore ☎ 7737669865 🥵 Book Your One night Stand

Call Girls In Bangalore ☎ 7737669865 🥵 Book Your One night Stand

(INDIRA) Call Girl Aurangabad Call Now 8617697112 Aurangabad Escorts 24x7

(INDIRA) Call Girl Aurangabad Call Now 8617697112 Aurangabad Escorts 24x7

The Most Attractive Pune Call Girls Budhwar Peth 8250192130 Will You Miss Thi...

The Most Attractive Pune Call Girls Budhwar Peth 8250192130 Will You Miss Thi...

Booking open Available Pune Call Girls Pargaon 6297143586 Call Hot Indian Gi...

Booking open Available Pune Call Girls Pargaon 6297143586 Call Hot Indian Gi...

Call Now ≽ 9953056974 ≼🔝 Call Girls In New Ashok Nagar ≼🔝 Delhi door step de...

Call Now ≽ 9953056974 ≼🔝 Call Girls In New Ashok Nagar ≼🔝 Delhi door step de...

Booking open Available Pune Call Girls Koregaon Park 6297143586 Call Hot Ind...

Booking open Available Pune Call Girls Koregaon Park 6297143586 Call Hot Ind...

Water Industry Process Automation & Control Monthly - April 2024

Water Industry Process Automation & Control Monthly - April 2024

Roadmap to Membership of RICS - Pathways and Routes

Roadmap to Membership of RICS - Pathways and Routes

Call for Papers - International Journal of Intelligent Systems and Applicatio...

Call for Papers - International Journal of Intelligent Systems and Applicatio...

Call Girls Wakad Call Me 7737669865 Budget Friendly No Advance Booking

Call Girls Wakad Call Me 7737669865 Budget Friendly No Advance Booking

xilinx fpga problems

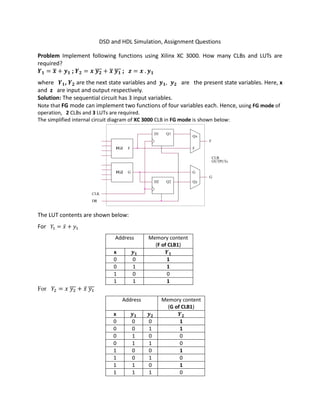

- 1. DSD and HDL Simulation, Assignment Questions Problem Implement following functions using Xilinx XC 3000. How many CLBs and LUTs are required? 𝒀 = 𝒙̅ + 𝒚 ; 𝒀 = 𝒙 𝒚̅̅̅ + 𝒙̅ 𝒚̅̅̅ ; 𝒛 = 𝒙 . 𝒚 where 𝒀 , 𝒀 are the next state variables and 𝒚 , 𝒚 are the present state variables. Here, x and z are input and output respectively. Solution: The sequential circuit has 3 input variables. Note that FG mode can implement two functions of four variables each. Hence, using FG mode of operation, 2 CLBs and 3 LUTs are required. The simplified internal circuit diagram of XC 3000 CLB in FG mode is shown below: The LUT contents are shown below: For = ̅ + Address Memory content (F of CLB1) x 𝒚 𝒀 0 0 1 0 1 1 1 0 0 1 1 1 For = ̅̅̅ + ̅ ̅̅̅ Address Memory content (G of CLB1) x 𝒚 𝒚 𝒀 0 0 0 1 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 1 1 1 1 0 DR CLB OUTPUTs G FG1 F Qy CLK GFG2 Q2 D1 F D2 G Q1 Qx F

- 2. For 𝑧 = . Address Memory content (F of CLB2) x 𝒚 𝒀 0 0 0 0 1 0 1 0 0 1 1 1 Circuit implementation using two XC3000 CLBs is shown below: ----------------------------------------------------------------------------------------------------------------------------------------- Problem Consider a 2 bit magnitude comparator to compare 𝐴 𝐴 and 𝐵 𝐵 to define three outputs A>B, A<B, A=B and map it using Xilinx XC 3000 FPGA. How many CLBs and LUTs are required? Show the contents of sRAM cell Solution: Consider the truth table for output A=B Y1 Q1 D2 Q1 Q2 Q2 DR G y1 CLK G G F Y2 G z FG2 FG1 CLB 2 x Qx y1 Qy DR x y1 CLB 1 y2 D2 FG1 F x F FG2 CLK Qy D1 D1 F Qx

- 3. 𝐴 𝐴 𝐵 𝐵 EQ 0 0 0 0 1 0 1 0 1 1 1 0 1 0 1 1 1 1 1 1 Design equation for EQ is 𝐸𝑄 = 𝐴̅̅̅ 𝐴̅̅̅ 𝐵̅̅̅ 𝐵̅̅̅ + 𝐴̅̅̅ 𝐴 𝐵̅̅̅ 𝐵 + 𝐴 𝐴̅̅̅ 𝐵 𝐵̅̅̅ + 𝐴 𝐴 𝐵 𝐵 Consider the truth table for output A>B 𝐴 𝐴 𝐵 𝐵 A>B 1 X 0 X 1 0 1 0 0 1 1 1 1 0 1 The corresponding implicant table is 𝐴 𝐴 𝐵 𝐵 A>B 1 X 0 X 1 X 1 0 0 1 1 1 X 0 1 Design equation for A>B is 𝐴 > 𝐵 = 𝐴 𝐵̅̅̅ + 𝐴 𝐵̅̅̅ 𝐵̅̅̅ + 𝐴 𝐴 𝐵̅̅̅ Consider the truth table for output A<B 𝐴 𝐴 𝐵 𝐵 A<B 0 X 1 X 1 0 0 0 1 1 1 0 1 1 1 The corresponding implicant table is 𝐴 𝐴 𝐵 𝐵 A<B 0 X 1 X 1 0 0 X 1 1 X 0 1 1 1 Design equation for A<B is 𝐴 < 𝐵 = 𝐴̅̅̅ 𝐵 + 𝐴̅̅̅. 𝐴̅̅̅̅. 𝐵 + 𝐴̅̅̅̅ 𝐵 𝐵

- 4. 2 bit magnitude comparator has 4 input variables and 3 outputs. The circuit implementation using XC 3000 in FG mode requires 2 CLBs and 3 LUTs. Circuit implementation using two XC3000 CLBs is shown below: The LUT (LUT1 and LUT2 of two CLBs) contents are given below: G A0 B1 LUT1 FG mode B0 F F A0 Qy Qy B1 CLK CLK G A>B G A1 A=B B1 Q2 Q2 A<B B0 D1 D1 A1 D2 D2 A0 Q1 Q1 B0 Qx Qx LUT2 F F FG mode DR CLB 1 LUT1 CLB 2 DR A1 LUT2 G

- 5. Address Memory content (F of CLB1) Memory content (G of CLB1) Memory content (F of CLB2) > = < 0 0 0 0 0 1 0 0 0 0 1 0 0 1 0 0 1 0 0 0 1 0 0 1 1 0 0 1 0 1 0 0 1 0 0 0 1 0 1 0 1 0 0 1 1 0 0 0 0 0 1 1 1 0 0 0 1 0 0 0 1 0 0 1 0 0 1 1 0 0 1 0 1 0 0 1 0 1 0 1 1 0 0 1 1 1 0 0 0 0 0 1 1 0 1 0 0 0 1 1 1 0 1 0 0 1 1 1 1 0 1 0 ------------------------------------------------------------------------------------------------------------------------------ Problem Implement following function using Xilinx XC 3000. How many CLBs and LUTs are required? F(a, b, c, d, e) = a. b. c + a. b̅. c + e̅ + d. e Solution: The output function has 5 input variables. The circuit implementation using XC 3000 in F mode (Note that F mode can generate one function of five variables) requires 1 CLB and 1 LUT. Problem Implement 2421 to 8421 code converter using Xilinx XC 3000. How many CLBs and LUTs are required? Show the contents of the sRAM cell. Dr. D. V. Kamath Professor, Dept. of E&C Engg., MIT LUT F F G b e Q2 DR CLB 1 Qy CLK D1 F F Qx Q1 G a D2 c d F mode