Flip flops: tipos D, JK e T

- 1. 1 FLIP FLOP`S Trabalho de SDAC Desenvolvido por: Fábio Guerreiro

- 2. 2 ÍNDICE Introduçao………………………………………..………………….…….…Pag.3 O que são Flip Flops………………………………………….…….…….Pag.4 Flip Flop D…………………………………………………………...….…….Pag.5 Flip Flop´s Jk………………………………………………...………….……Pag.6 Flip Flop´s T.......................................................................Pag.7 Contador em anel – “Ring Counter”……………………………...Pag.8 CONTADOR EM ANEL: LOCKOUT……………………………………Pag.9 Contador assincrono…………………………………………………….Pag.10 Contador sincrono………………………………………………………..Pag.11 Web grafia…………………………………………………………………….Pag.12

- 3. 3 INTRODUÇAO Este trabalho foi desenvolvido no âmbito da disciplina de SDAC, e com este trabalho pretendo saber o que sao flip flops do tipo D ,T e JK ,para que servem e quais as tabelas de verdade que os representam.

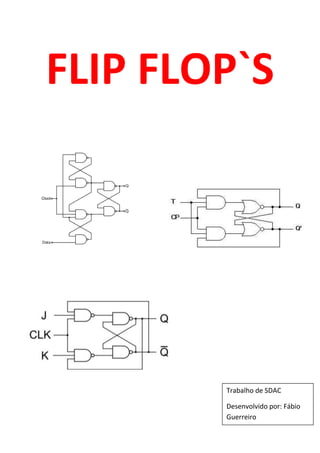

- 4. 4 O QUE SÃO FLIP FLOP´S Os flip-flops são circuitos derivados dos latches, porem activados pela transição do sinal de controlo. Isso faz com que um flip-flop permaneça activado apenas durante um intervalo de tempo muito pequeno, após a ocorrência de uma transição do sinal de controlo. Nesse caso, uma eventual troca de estado só pode ocorrer durante esse breve intervalo de tempo em que o flip-flop está activado. Entre duas transições sucessivas do mesmo tipo (ou subida ou descida) do sinal de controlo, o flip-flop mantém o último estado adquirido. FLIP FLOP D

- 5. 5 O 'Flip-Flop D' possui uma entrada ligada directamente à saída (Q). Independentemente do estado actual de Q, este terá o valor 1 se D = 1 ou valor 0 se D = 0 quando ocorrer o impulso positivo do relógio (positive edge triggered). A informação é colocada na saída um ciclo depois de ela chegar à entrada. Este dispositivo é uma célula de memória básica (guarda um bit) e pode ser interpretado como uma linha de atraso primitiva (hold) de ordem zero. FLIP FLOP JK

- 6. 6 Esse circuito é formado por dois latches, denominados mestres (master) e escravo (slave). Possui a mesma tabela de combinações que o flip-flop J-K (edge- triggered), mas com convenções de tempos tne t tn+1 diferentes. JN, Kne Correspondem aos valores de J, K e Q no tempo imediatamente anterior a subida do pulso, enquanto Qn+1corresponde a saída no tempo posterior a descida do pulso Tabela de verdade: Circuito logico: FLIP FLOP T

- 7. 7 Se a entrada T estiver em estado alto, o flip-flop T (toggle) inverte seu estado sempre que a entrada de clock sofrer uma modificação. Se a entrada T foi baixa, o flip-flop mantém o valor do seu estado. A equação do flip flop T é: Tabela de verdade: Circuito logico: CONTADOR EM ANEL– “RING COUNTER”

- 8. 8 CONTADOR EM ANEL: LOCKOUT

- 10. 10 Os Flip-Flops não m damu de estado com o mesmo sincronismo sincronismo; – O CLK é colocado apenas no primeiro FF (LSB); – Há um pequeno atraso entre as mudanças de estado de cada FF; – O atraso é propagado de acordo com o número de FF conectados em cascata. CONTADOR SINCRONO

- 11. 11 Os Flip Os Flip-Flops mudam de estado com o mesmo sincronismo; Flops mudam de estado com o mesmo sincronismo; – O mesmo CLK é ligado em todos os FFs; – Há um atraso entre as mudanças de estado de cada FF; – O atraso não é propagado de acordo com o número de FF. WEB GRAFIA