Melden

Teilen

Downloaden Sie, um offline zu lesen

Empfohlen

Empfohlen

Weitere ähnliche Inhalte

Was ist angesagt?

Was ist angesagt? (20)

Hypervisor-Based Secure Cockpit Using on-SoC Separated Core

Hypervisor-Based Secure Cockpit Using on-SoC Separated Core

DESIGN CHOICES FOR EMBEDDED REAL-TIME CONTROL SYSTEMS @ 4th FPGA Camp

DESIGN CHOICES FOR EMBEDDED REAL-TIME CONTROL SYSTEMS @ 4th FPGA Camp

Aewin network security appliance network management platform_scb6982

Aewin network security appliance network management platform_scb6982

Catálogo DDC con bus de datos y software para aeronáutica

Catálogo DDC con bus de datos y software para aeronáutica

FIELD PROGRAMMABLE GATE ARRAYS AND THEIR APPLICATIONS

FIELD PROGRAMMABLE GATE ARRAYS AND THEIR APPLICATIONS

Andere mochten auch

Andere mochten auch (20)

Lineamientos curriculares en lengua castellana capítulo 2

Lineamientos curriculares en lengua castellana capítulo 2

Ähnlich wie Project poster: SDR universal platform

This session includes a discussion on rapid prototyping concepts using Xilinx All Programmable FPGAs and SoCs with Analog Devices high speed and precision products. Covered in this session will be common use cases for Xilinx devices in DSP applications that interface to high speed analog. An overview will be provided of how Xilinx accelerates development with DSP platforms that can be used to quickly evaluate and prototype systems that include high speed analog, programmable logic, and embedded processing. Also covered will be an introduction to Xilinx’s new Vivado Design Suite development environment that shortens design cycles by providing an IP centric design flow, easy to use design analysis and debug, and high level design flows supporting C/C++ and MATLAB/Simulink.High Performance DSP with Xilinx All Programmable Devices (Design Conference ...

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...Analog Devices, Inc.

Various approaches have been developed for integrating FPGA and GPP application components in a Software Communications Architecture (SCA) radio. Most of these have been less than successful, primarily due to overhead, latency and/or maintainability issues. Spectra IP Core is a second-generation solution to FPGA-GPP component integration that provides a low-latency, standards-based CORBA protocol with excellent performance metrics and the robustness of a proven, deployed solution. Building on PrismTech’s ICO v1, Spectra IP Core is a second-generation COTS product. This webcast will introduce the Spectra IP Core architecture, its main functions and its performance benchmarks. Although FPGA ‘middleware’ is a new concept for many FPGA developers, the capabilities provided by Spectra IP Core not only provide valuable integration ‘hooks’, but also help support a highly-efficient, proven radio component that simplifies the integration of high-level software development with digital design and accelerates the development of SCA-compliant FPGA components for SCA radios. These slides will be of great interest and value to project managers, systems engineers and architects as well as software and digital engineers involved in designing, building and testing SCA-compliant SDRs.Spectra IP Core ORB - high-performance, low-latency solution for FPGA-GPP com...

Spectra IP Core ORB - high-performance, low-latency solution for FPGA-GPP com...ADLINK Technology IoT

Ähnlich wie Project poster: SDR universal platform (20)

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...

Design and Implementation of FPGA Based Signal Processing Card

Design and Implementation of FPGA Based Signal Processing Card

Spectra IP Core ORB - high-performance, low-latency solution for FPGA-GPP com...

Spectra IP Core ORB - high-performance, low-latency solution for FPGA-GPP com...

Mehr von Bertalan EGED

Mehr von Bertalan EGED (16)

Kürzlich hochgeladen

Kürzlich hochgeladen (20)

Repurposing LNG terminals for Hydrogen Ammonia: Feasibility and Cost Saving

Repurposing LNG terminals for Hydrogen Ammonia: Feasibility and Cost Saving

TrustArc Webinar - Unlock the Power of AI-Driven Data Discovery

TrustArc Webinar - Unlock the Power of AI-Driven Data Discovery

How to Troubleshoot Apps for the Modern Connected Worker

How to Troubleshoot Apps for the Modern Connected Worker

AI+A11Y 11MAY2024 HYDERBAD GAAD 2024 - HelloA11Y (11 May 2024)

AI+A11Y 11MAY2024 HYDERBAD GAAD 2024 - HelloA11Y (11 May 2024)

Connector Corner: Accelerate revenue generation using UiPath API-centric busi...

Connector Corner: Accelerate revenue generation using UiPath API-centric busi...

Apidays New York 2024 - Scaling API-first by Ian Reasor and Radu Cotescu, Adobe

Apidays New York 2024 - Scaling API-first by Ian Reasor and Radu Cotescu, Adobe

DEV meet-up UiPath Document Understanding May 7 2024 Amsterdam

DEV meet-up UiPath Document Understanding May 7 2024 Amsterdam

Apidays New York 2024 - The Good, the Bad and the Governed by David O'Neill, ...

Apidays New York 2024 - The Good, the Bad and the Governed by David O'Neill, ...

Six Myths about Ontologies: The Basics of Formal Ontology

Six Myths about Ontologies: The Basics of Formal Ontology

"I see eyes in my soup": How Delivery Hero implemented the safety system for ...

"I see eyes in my soup": How Delivery Hero implemented the safety system for ...

ICT role in 21st century education and its challenges

ICT role in 21st century education and its challenges

Strategies for Landing an Oracle DBA Job as a Fresher

Strategies for Landing an Oracle DBA Job as a Fresher

Vector Search -An Introduction in Oracle Database 23ai.pptx

Vector Search -An Introduction in Oracle Database 23ai.pptx

Apidays New York 2024 - APIs in 2030: The Risk of Technological Sleepwalk by ...

Apidays New York 2024 - APIs in 2030: The Risk of Technological Sleepwalk by ...

Cloud Frontiers: A Deep Dive into Serverless Spatial Data and FME

Cloud Frontiers: A Deep Dive into Serverless Spatial Data and FME

Project poster: SDR universal platform

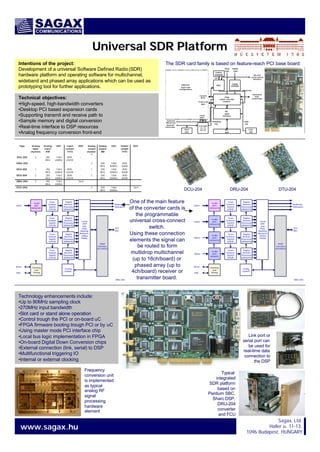

- 1. www.www.sagaxsagax..huhu SagaxSagax,, LtdLtd.. HallerHaller u. 11-13.u. 11-13. 1096 Budapest, HUNGARY1096 Budapest, HUNGARY Universal SDR PlatformUniversal SDR Platform Intentions of the project: Development of a universal Software Defined Radio (SDR) hardware platform and operating software for multichannel, wideband and phased array applications which can be used as prototyping tool for further applications. Technical objectives: •High-speed, high-bandwidth converters •Desktop PCI based expansion cards •Supporting transmit and receive path to •Sample memory and digital conversion •Real-time interface to DSP resources •Analog frequency conversion front-end PCI HOST Interface PCI BUS FPGA LOGIC and DSP resource MCU Config EEPROM Control EEPROM PROM JTAG FPGA JTAG Dedicated data connection RS-232 serial control interface Front-end BUS Control BUS CLK DRV /2, /4 X2, X4SCLK OSC External CLK in/out LCLK OSC Sampling CLK Local CLK I2C FPGA CFG Clock lines Different front-end configurations External TRG in/out The SDR card family is based on feature-reach PCI base board: 14-Bit ADC (AD6644) Clocking and Timing Cross Connect Switch (CPLD) Cross Connect Switch (CPLD) Cross Connect Switch (CPLD) Cross Connect Switch (CPLD) Digital Receive Processor (AD6624) Digital Receive Processor (AD6624) Digital Receive Processor (AD6624) Digital Receive Processor (AD6624) Local DSP and Data Routing Resource (Xilinx FPGA) HOST Interface (PLX9054) PCI Bus RCh1 RCLK Config Control TRG DRU-204 Dedicted Data ports 14-Bit ADC (AD664) 14-Bit ADC (AD6644) 14-Bit ADC (AD6644) 14-Bit ADC (AD6644) Clocking and Timing Cross Connect Switch (CPLD) Cross Connect Switch (CPLD) Cross Connect Switch (CPLD) Cross Connect Switch (CPLD) Digital Receive Processor (AD6624) Digital Receive Processor (AD6624) Digital Receive Processor (AD6624) Digital Receive Processor (AD6624) Local DSP and Data Routing Resource (Xilinx FPGA) HOST Interface (PLX9054) PCI Bus RCh1 RCh2 RCh3 RCh4 RCLK Config Control Dedicted Data ports TRG DRU-204 One of the main feature of the converter cards is the programmable universal cross-connect switch. Using these connection elements the signal can be routed to form multidrop multichannel (up to 16ch/board) or phased array (up to 4ch/board) receiver or transmitter board. Link port or serial port can be used for real-time data connection to the DSP Technology enhancements include: •Up to 80MHz sampling clock •270MHz input bandwidth •Slot card or stand alone operation •Control trough the PCI or on-board uC •FPGA firmware booting trough PCI or by uC •Using master mode PCI interface chip •Local bus logic implementation in FPGA •On-board Digital Down Conversion chips •External connection (link, serial) to DSP •Multifunctional triggering IO •Internal or external clocking Type Analog input channels Analog input BW ADC Input sample FIFO DDC Analog output channel s Analog output BW DAC Output sample FIFO DUC DIU-202 2 250 MHz 14bit 65MHz 2KW- 65KW - DOU-202 2 300 MHz 14bit 80MHz 2KW- 65KW - DCU-202 1 250 MHz 14bit 65MHz 2KW- 65KW - 1 300 MHz 14bit 80MHz 2KW- 65KW - DCU-204 2 250 MHz 14bit 65MHz 2KW- 65KW - 2 300 MHz 14bit 80MHz 2KW- 65KW - DRU-204 4 250 MHz 14bit 65MHz - 16ch DTU-204 4 300 MHz 14bit 80MHz - 16ch DCU-204 DRU-204 DTU-204 Typical integrated SDR platform based on Pentium SBC, Sharc DSP, DRU-204 converter and FCU Frequency conversion unit is implemented as typical analog RF signal processing hardware element