DiagramsOS.pdf

•

0 gefällt mir•9 views

Diagram of OS Stallings, Chp 1 to chp 9

Melden

Teilen

Melden

Teilen

Downloaden Sie, um offline zu lesen

Empfohlen

Empfohlen

Weitere ähnliche Inhalte

Ähnlich wie DiagramsOS.pdf

Ähnlich wie DiagramsOS.pdf (20)

Cpu register, instruction exucution and interrupts unit 1 by ram k paliwal

Cpu register, instruction exucution and interrupts unit 1 by ram k paliwal

Interrupts on 8086 microprocessor by vijay kumar.k

Interrupts on 8086 microprocessor by vijay kumar.k

PLC SCUBE STANDARD PROGRAMING EMERSON EDUARDO RODRIGUES

PLC SCUBE STANDARD PROGRAMING EMERSON EDUARDO RODRIGUES

Kürzlich hochgeladen

Kürzlich hochgeladen (20)

%+27788225528 love spells in new york Psychic Readings, Attraction spells,Bri...

%+27788225528 love spells in new york Psychic Readings, Attraction spells,Bri...

Large-scale Logging Made Easy: Meetup at Deutsche Bank 2024

Large-scale Logging Made Easy: Meetup at Deutsche Bank 2024

OpenChain - The Ramifications of ISO/IEC 5230 and ISO/IEC 18974 for Legal Pro...

OpenChain - The Ramifications of ISO/IEC 5230 and ISO/IEC 18974 for Legal Pro...

W01_panagenda_Navigating-the-Future-with-The-Hitchhikers-Guide-to-Notes-and-D...

W01_panagenda_Navigating-the-Future-with-The-Hitchhikers-Guide-to-Notes-and-D...

+971565801893>>SAFE AND ORIGINAL ABORTION PILLS FOR SALE IN DUBAI AND ABUDHAB...

+971565801893>>SAFE AND ORIGINAL ABORTION PILLS FOR SALE IN DUBAI AND ABUDHAB...

Devoxx UK 2024 - Going serverless with Quarkus, GraalVM native images and AWS...

Devoxx UK 2024 - Going serverless with Quarkus, GraalVM native images and AWS...

%in ivory park+277-882-255-28 abortion pills for sale in ivory park

%in ivory park+277-882-255-28 abortion pills for sale in ivory park

8257 interfacing 2 in microprocessor for btech students

8257 interfacing 2 in microprocessor for btech students

%+27788225528 love spells in Boston Psychic Readings, Attraction spells,Bring...

%+27788225528 love spells in Boston Psychic Readings, Attraction spells,Bring...

%+27788225528 love spells in Atlanta Psychic Readings, Attraction spells,Brin...

%+27788225528 love spells in Atlanta Psychic Readings, Attraction spells,Brin...

%in tembisa+277-882-255-28 abortion pills for sale in tembisa

%in tembisa+277-882-255-28 abortion pills for sale in tembisa

WSO2Con2024 - WSO2's IAM Vision: Identity-Led Digital Transformation

WSO2Con2024 - WSO2's IAM Vision: Identity-Led Digital Transformation

WSO2Con2024 - From Code To Cloud: Fast Track Your Cloud Native Journey with C...

WSO2Con2024 - From Code To Cloud: Fast Track Your Cloud Native Journey with C...

%in Rustenburg+277-882-255-28 abortion pills for sale in Rustenburg

%in Rustenburg+277-882-255-28 abortion pills for sale in Rustenburg

%in tembisa+277-882-255-28 abortion pills for sale in tembisa

%in tembisa+277-882-255-28 abortion pills for sale in tembisa

Payment Gateway Testing Simplified_ A Step-by-Step Guide for Beginners.pdf

Payment Gateway Testing Simplified_ A Step-by-Step Guide for Beginners.pdf

WSO2CON 2024 - Cloud Native Middleware: Domain-Driven Design, Cell-Based Arch...

WSO2CON 2024 - Cloud Native Middleware: Domain-Driven Design, Cell-Based Arch...

DiagramsOS.pdf

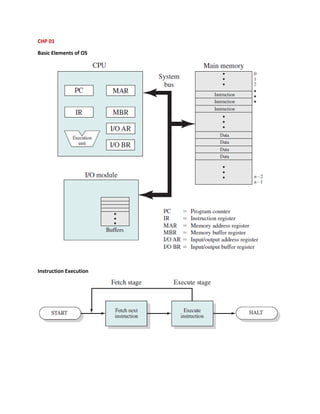

- 1. CHP 01 Basic Elements of OS Instruction Execution

- 2. Instruction Cycle with Interrupts Interrupt Processing

- 3. Interrupts User Program WRITE WRITE WRITE I/O Program I/O Command END 1 2 3 2 3 4 5 (a) No interrupts = interrupt occurs during course of execution of user program User Program WRITE WRITE WRITE I/O Program I/O Command Interrupt Handler END 1 2a 2b 3a 3b 4 5 (b) Interrupts; short I/O wait User Program WRITE WRITE WRITE 1 (c) Interrupts; lo Figure 1.5 Program Flow of Control Without and With In User Program WRITE WRITE WRITE I/O Program I/O Command END 1 2 3 2 3 4 5 (a) No interrupts = interrupt occurs during course of execution of user program User Program WRITE WRITE WRITE I/O Program I/O Command Interrupt Handler END 1 2a 2b 3a 3b 4 5 (b) Interrupts; short I/O wait User Program WRITE WRITE WRITE 1 (c) Interrupts Figure 1.5 Program Flow of Control Without and With

- 5. CHP 02 The Operating System as a User/Computer Interface A view of operating system services

- 6. The Operating System as Resource Manager Typical process implementation

- 7. Key Elements of an Operating System for multiprogramming Simple Batch Processing System CHP 3

- 8. Process Control Block Two-State Process Model Queuing Diagram c

- 9. Five State Process Model Using Two Queues One Suspend State

- 10. Multiple Blocked Queues Two Suspend State

- 11. OS Control Tables Structure of Process image in Virtual Memory

- 13. Threads vs Processes Types of Parallelism (Data and Task)

- 14. ULT, KLT & Combined Relationships between ULT States and Process States

- 15. CHP 7 Addressing Requirements for a Process Hardware Support for Relation Process Control Block Program Data Stack Current top of stack Entry point to program Process control information Increasing address values Branch instruction Reference to data Figure 7.1 Addressing Requirements for a Process Process Control Block Program Data Stack Figure 7.8 Hardware Support for Relocation Comparator Interrupt to operating system Absolute address Process image in main memory Relative address Base Register Bounds Register Adder

- 16. CHP 8 Address Translation in a Paging System Use of a Translation Lookaside Buffer

- 17. Operation of Paging and Translation Lookaside Buffer