Instrucciones avr

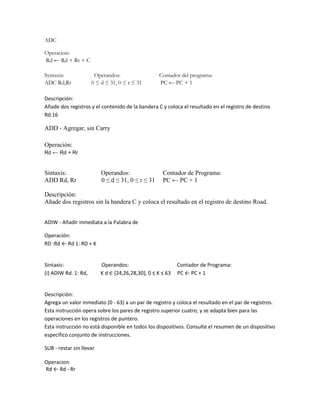

- 1. ADC Operacion: Rd ← Rd + Rr + C Syntaxis: Operandos: Contador del programa: ADC Rd,Rr 0 ≤ d ≤ 31, 0 ≤ r ≤ 31 PC ← PC + 1 Descripción: Añade dos registros y el contenido de la bandera C y coloca el resultado en el registro de destino Rd.16 ADD - Agregar, sin Carry Operación: Rd ← Rd + Rr Sintaxis: Operandos: Contador de Programa: ADD Rd, Rr 0 ≤ d ≤ 31, 0 ≤ r ≤ 31 PC ← PC + 1 Descripción: Añade dos registros sin la bandera C y coloca el resultado en el registro de destino Road. ADIW - Añadir inmediata a la Palabra de Operación: RD :Rd ← Rd 1: RD + K Sintaxis: Operandos: Contador de Programa: (i) ADIW Rd. 1: Rd, K d ∈ {24,26,28,30}, 0 ≤ K ≤ 63 PC ← PC + 1 Descripción: Agrega un valor inmediato (0 - 63) a un par de registro y coloca el resultado en el par de registros. Esta instrucción opera sobre los pares de registro superior cuatro, y se adapta bien para las operaciones en los registros de puntero. Esta instrucción no está disponible en todos los dispositivos. Consulte el resumen de un dispositivo específico conjunto de instrucciones. SUB - restar sin llevar Operacion: Rd ← Rd - Rr

- 2. Syntaxis: Operandos: Contador del Programa: SUB Rd,Rr 0 ≤ d ≤ 31, 0 ≤ r ≤ 31 PC ← PC + 1 Descripción: Resta dos registros y coloca el resultado en la Calle de registro de destino. SUBI - Restar inmediata Operación: (i) Rd ← Rd - K Syntaxis: Operandos: Contador del Programa: (i) SUBI Rd,K 16 ≤ d ≤ 31, 0 ≤ K ≤ 255 PC ← PC + 1 Descripción: Resta un registro y una constante y coloca el resultado en el registro de destino "Rd". Esta instrucción se está trabajando en el Registro R16 a R31 y está muy bien adaptado para las operaciones en la X, Y y Z de los punteros. SBC - Resta con Carry Operación: (i) Rd ← Rd - Rr - C Syntaxis: Operandos: Contador del Programa: (i) SBC Rd,Rr 0 ≤ d ≤ 31, 0 ≤ r ≤ 31 PC ← PC + 1 Descripción: Resta dos registros y resta con la bandera C y coloca el resultado en la Calle de registro de destino. SBCI - Resta inmediato con Carry Operación: (i) Rd ← Rd - K - C Syntaxis: Operandos: Contador del Programa: (i) SBCI Rd,K 16 ≤ d ≤ 31, 0 ≤ K ≤ 255 PC ← PC + 1 Descripción: Resta una constante a partir de un registro y resta con la bandera C y coloca el resultado en el registro de destino "Rd". SBIW - Restar inmediata de la Palabra Operación:

- 3. (i) Rd+1:Rd ← Rd+1:Rd - K Syntaxis: Operandos: Contador del Programa: (i) SBIW Rd+1:Rd, K d ∈ {24,26,28,30}, 0 ≤ K ≤ 63 PC ← PC + 1 Descripción: Resta un valor inmediato (0-63) a partir de un par de registro y coloca el resultado en el par de registros. Esta instrucción opera sobre los pares de registro superior cuatro, y se adapta bien para las operaciones en los Registros de puntero. Esta instrucción no está disponible en todos los dispositivos. Consulte el resumen de un dispositivo específico conjunto de instrucciones. AND – y Logica Operación: Rd ← Rd • Rr Sintaxis: Operandos: Contador de Programa: AND Rd,Rr 0 ≤ d ≤ 31, 0 ≤ r ≤ 31 PC ← PC + 1 Descripción: Realiza la operación lógica AND entre el contenido del registro Rd y Rr registro y coloca el resultado en el registro de destino "Rd". ANDI - lógica y inmediata Operación: (i) Rd ← Rd • K Sintaxis: Operandos: Contador de Programa: (i) ANDI Rd,K 16 ≤ d ≤ 31, 0 ≤ K ≤ 255 PC ← PC + 1 Descripción: Realiza la operación lógica AND entre el contenido del registro Rd. y una constante y coloca el resultado en el destino registro "Rd". OR - OR lógico Operación: (i) Rd ← Rd v Rr Sintaxis: Operandos: Contador de Programa: (i) OR Rd, Rr 0 ≤ d ≤ 31, 0 ≤ r ≤ 31 PC ← PC + 1 Descripción: Realiza la operación lógica OR entre el contenido del registro Rd y Rr registro y coloca el resultado en el registro de destino "Rd".

- 4. ORI - O lógico inmediata Operación: (i) Rd ← Rd v K Sintaxis: Operandos: Contador de Programa: (i) ORI Rd, K 16 ≤ d ≤ 31, 0 ≤ K ≤ 255 PC ← PC + 1 Descripción: Realiza la operación lógica OR entre el contenido del registro Rd. y una constante y coloca el resultado en el registro de destino "Rd". EOR - OR exclusivo Operación: (i) RD ← Rd. ⊕ Rr Sintaxis: Operandos: Contador de Programa: (i) EOR Rd., RR 0 ≤ d ≤ 31, 0 ≤ r ≤ 31 PC ← PC + 1 Descripción: Lleva a cabo la recuperación asistida del OR exclusivo entre el contenido del registro Rd y Rr registro y coloca el resultado en el registro de destino "Rd". COM - complemento a uno. Operación: (i) Rd ← $ FF - Rd. Sintaxis: Operandos: Contador de Programa: (i) COM Rd. 0 ≤ d ≤ 31 PC ← PC + 1 Descripción: Esta instrucción se lleva a cabo un complemento Uno de registro Rd. NEG - el complemento a dos Operación: (i) RD ← $ 00 - Calle Sintaxis: Operandos: Contador de Programa: (i) NEG Rd. 0 ≤ d ≤ 31 PC ← PC + 1 Descripción: Reemplaza el contenido del registro Rd con complemento de sus dos mujeres; el valor de $ 80 se mantiene sin cambios. SBR - conjunto de bits en el Registro .

- 5. Operación: (i) RD ← Rd. v K Sintaxis: Operandos: Contador de Programa: (i) SBR Rd, K 16 ≤ d ≤ 31, 0 ≤ K ≤ 255 PC ← PC + 1 Descripción: Establece bits especificado en el registro Rd.. Realiza la lógica ORI entre el contenido del registro Rd. y una máscara constante K y coloca el resultado en RD registro de destino CBR - Borrar los bits en el Registro Operación: (i) R Rd. ← Road • ($ FF - K) Sintaxis: Operandos: Contador de Programa: (i) CBR Rd, K 16 ≤ d ≤ 31, 0 ≤ K ≤ 255 PC ← PC 1 Descripción: Borra los bits especificado en el registro Rd.. Realiza la. Lógica AND entre el contenido del registro Rd. y el complemento de la constante K. máscara se coloca El resultado en el registro Rd. INC - Incremento de Operación: (i) R Rd. ← Rd 1 Sintaxis: Operandos: Contador de Programa: (i) INC Rd. 0 ≤ d ≤ 31 PC ← PC 1 Descripción: Añade un -1 - para el contenido del registro Rd. y coloca el resultado en el registro de destino Rd.. La bandera C en SREG no se ve afectada por la operación, permitiendo así que la instrucción INC para ser utilizado en un contador de bucle en los cálculos de precisión múltiple. Cuando se opera en números sin signo, sólo ramas BREQ y Brne se puede esperar que un rendimiento consistente. Cuando se trabaja con valores de complemento a dos, todas las ramas firmados están disponibles DEC - Decremento Operación: (i) Rd. ← Rd. - 1

- 6. Sintaxis: Operandos: Contador de Programa: (i) DEC Rd. 0 ≤ d ≤ 31 PC ← PC 1 Descripción: Resta un -1 - de los contenidos de registro Rd. y coloca el resultado en el registro de destino Road. La bandera C en SREG no se ve afectada por la operación, permitiendo así que la instrucción diciembre para ser utilizado en un contador de bucle en los cálculos de precisión múltiple. Cuando se opera en valores sin signo, sólo ramas BREQ y Brne se puede esperar que un rendimiento consistente. Cuando se trabaja con valores de complemento a dos, todas las ramas firmados están disponibles. TST - Prueba de cero o Menos Operación: (i) R Rd. ← Rd. • RD Sintaxis: Operandos: Contador de Programa: (i) TST Rd. 0 ≤ d ≤ 31 PC ← PC 1 Descripción: Comprueba si un registro es cero o negativo. Realiza una operación lógica AND entre un registro y sí mismo. El registro se mantendrá sin cambios. CLR - Claro Registrarse Operación: (i) R Rd. ← Rd. ⊕ Rd. Sintaxis: Operandos: Contador de Programa: (i) CLR Rd. 0 ≤ d ≤ 31 PC ← PC 1 Descripción: Borra un registro. Esta instrucción realiza un OR exclusivo entre un registro y sí mismo. Esto borrará todos los bits en el registro. SER - Establecer todos los bits del registro Operación: (i) Rd ← $ FF Sintaxis: Operandos: Contador de Programa: (i) SER Rd. 16 ≤ d ≤ 31 PC ← PC 1 Descripción: Carga $ FF directamente al registro de Calle. MUL - Multiplicar sin firmar

- 7. Operación: (i) R1: R0 ← Rd. × RR (sin signo ← sin signo x signo) Sintaxis: Operandos: Contador de Programa: (i) MUL Rd., RR 0 ≤ d ≤ 31, 0 ≤ r ≤ 31 PC ← PC 1 Descripción: Esta instrucción realiza de 8-bits x 8-bits → 16-bits sin signo de multiplicación. El RD multiplicando y el multiplicador del RR son dos registros que contienen números sin signo. El producto entero de 16 bits se encuentra en R1 (byte alto) y R0 (low). Tenga en cuenta que si el multiplicando o el multiplicador se selecciona de R0 o R1 el resultado se sobreponen a los que después de la multiplicación. Esta instrucción no está disponible en todos los dispositivos. Consulte el resumen de un dispositivo específico conjunto de instrucciones. Muls - Multiplicar con signo Operación: (I) R1: R0 ← Rd. × Rr (firmado ← firmado × firmado) Sintaxis: Operandos: Contador de Programa: (I) Muls Rd, Rc 16 ≤ d ≤ 31, 16 ≤ r ≤ 31 PC ← PC 1 Descripción: Esta instrucción realiza de 8-bits x 8-bits → 16-bits multiplicación firmado. El RD multiplicando y el multiplicador del RR son dos registros que contienen números con signo. El producto de 16 bits con signo se coloca en R1 (byte alto) y R0 (low). Esta instrucción no está disponible en todos los dispositivos. Consulte el resumen de un dispositivo específico conjunto de instrucciones. MULSU - Multiplicar Firmado con Unsigned Operación: (I) R1: R0 ← Rd. × Rr (firmado ← firmado × sin signo) Sintaxis: Operandos: Contador de Programa: (I) MULSU Rd, Rc 16 ≤ d ≤ 23, 16 ≤ r ≤ 23 PC ← PC 1 Descripción: Esta instrucción realiza de 8-bits x 8-bits → 16-bits multiplicación de una firma y un número sin signo. El RD multiplicando y el multiplicador del RR son dos registros. El RD multiplicando es un número con signo, y el multiplicador Rr no tiene signo. El producto de 16 bits con signo se coloca en R1 (byte alto) y R0 (low). Esta instrucción no está disponible en todos los dispositivos. Consulte el resumen de un dispositivo específico conjunto de instrucciones. FMUL - Unsigned Multiplicar fraccional

- 8. Operación: (I) R1: R0 ← Rd. × RR (sin signo (1,15) ← sin signo (1,7) × sin signo (1.7)) Sintaxis: Operandos: Contador de Programa: (I) FMUL Rd., Rr 16 ≤ d ≤ 23, 16 ≤ r ≤ 23 PC ← PC 1 Descripción: Esta instrucción se lleva a cabo de 8-bits x 8-bit → 16-bit sin signo de multiplicación y cambia el resultado de un bit a la izquierda. Sea (NQ) indican un número fraccionario con los dígitos binarios de N a la izquierda del punto de base, y los dígitos binarios Q derecha del punto de base. Una multiplicación de dos números en los formatos (N1.Q1) y (N2.Q2) resultados en el formato ((N1, N2). FMULS - Multiplicar fraccional Firmado Operación: (I) R1: R0 ← Rd. × Rr (firmado (1,15) ← firmado (1,7) × firmado (1,7)) Sintaxis: Operandos: Contador de Programa: (I) FMULS Rd, Rc 16 ≤ d ≤ 23, 16 ≤ r ≤ 23 PC ← PC + 1 Descripción: Esta instrucción se lleva a cabo de 8-bits x 8-bit → 16-bit de multiplicación firmado y cambia el resultado de un bit a la izquierda. Sea (NQ) indican un número fraccionario con los dígitos binarios de N a la izquierda del punto de base, y los dígitos binarios Q derecha del punto de base. Una multiplicación de dos números en los formatos (N1.Q1) y (N2.Q2) resultados en el formato ((N1 + N2). (Q1 + Q2)). FMULSU - Multiplicar fraccional Firmado con Unsigned. Operación: (i) R1: R0 ← Rd. × Rr (firmado (1,15) ← firmado (1,7) × sin signo (1.7)) Sintaxis: Operandos: Contador de Programa: (i) FMULSU Rd, Rc 16 ≤ d ≤ 23, 16 ≤ r ≤ 23 PC ← PC 1 Descripción: Esta instrucción se lleva a cabo de 8-bits x 8-bit → 16-bit de multiplicación firmado y cambia el resultado de un bit a la izquierda. Sea (NQ) indican un número fraccionario con los dígitos binarios de N a la izquierda del punto de base, y los dígitos binarios Q derecha del punto de base. Una multiplicación de dos números en los formatos (N1.Q1) y (N2.Q2) resultados en el formato ((N1, N2). (T1 T2)) DES - Data Encryption Standard. Operación: (i) Si H = 0, entonces Cifrar ronda (R7-R0, R15-R8, K)

- 9. Si H = 1 entonces descifrar ronda (R7-R0, R15-R8, K) Sintaxis: Operandos: Contador de Programa: (i) DES 0x00 K ≤ K ≤ 0x0F PC ← PC 1 Descripción: El módulo es una extensión del conjunto de instrucciones a la CPU AVR, la realización de iteraciones DES. El bloque 64-bit de datos (texto o texto cifrado) se coloca en el archivo de registro de la CPU, registros R0-R7, donde LSB de datos se colocan en LSB de R0 y MSB de datos se colocan en MSB de R7. El total de 64-bits (incluyendo los bits de paridad) se coloca en los registros R8-R15, organizado en el archivo de registro con el LSB de clave en la LSB y MSB de la R8 de la clave en el MSB del R15. Ejecución de una instrucción DES realizará un ciclo en el algoritmo DES. Dieciséis rondas deben ser ejecutadas en orden creciente para formar la correcta cifrado DES o texto plano. Los resultados intermedios se almacenan en el registro de archivo (R0-R15) operando DES de instrucciones (K) determina que todo se ejecuta, y la bandera de acarreo de la mitad (H) determina si el cifrado o descifrado se realiza Instrucciones de salto RJMP - salto relativo Operación: (I) PC ← PC + k + 1 Sintaxis: Operandos: Contador de Programa: Pila (I) RJMP k-2 K ≤ k <2K PC ← PC + k + 1 sin cambios Descripción: Salto relativo a una dirección dentro de PC - 2K +1 y PC + 2K (palabras). Para los microcontroladores AVR con memoria de programa que no exceda de 4 K palabras (8K bytes) esta instrucción puede abordar toda la memoria de todas las ubicaciones de direcciones. Véase también el JMP. IJMP - salto indirecto Operación: (I) ← PC Z (15:00) Los dispositivos con PC de 16 bits, el máximo de 128 Kb de memoria de programa. (Ii) PC (15:00) ← Z (15:00) Los dispositivos con PC 22 bits, bytes Programa 8M de memoria máxima. PC (21:16) ← 0 Sintaxis: Operandos: Contador de Programa: Pila: (I), (ii) Ninguna IJMP Consulte Operación no afectada Descripción: Salto indirecto a la dirección apuntada por la Z (16 bits) un registro puntero en el archivo de Registro. El Registro de Z-puntos es de 16 bits de ancho y permite saltar dentro de los más bajos

- 10. palabras 64K (128K bytes) parte de la memoria de programa. Esta instrucción no está disponible en todos los dispositivos. Consulte el resumen de un dispositivo específico conjunto de instrucciones. EIJMP - salto indirecto extendido Operación: PC (15:00) ← Z (15:00) PC (21:16) ← Eind Sintaxis: Operandos: Contador de Programa: Pila: (I) Ninguna EIJMP Consulte Operación no afectada Descripción: Salto indirecto a la dirección apuntada por la Z (16 bits) un registro puntero en el Archivo de Registro y el Registro Eind en el espacio de E / S. Esta instrucción permite saltos indirectos a la totalidad 4M (palabras) el espacio de memoria del programa. Véase también IJMP. Esta instrucción no está disponible en todos los dispositivos. Consulte el resumen de un dispositivo específico conjunto de instrucciones. JMP - Saltar. Operación: (I) ← PC k Sintaxis: Operandos: Contador de Programa: Pila: (I) JMP k 0 ≤ k <k PC ← 4M sin cambios Descripción: Ir a una dirección dentro de la totalidad 4M (palabras) de memoria de programa. Véase también RJMP. Esta instrucción no está disponible en todos los dispositivos. Consulte el resumen de un dispositivo específico conjunto de instrucciones Rcall - Convocatoria relativa a la subrutina Operación: (I) PC ← PC + k + 1 Los dispositivos con PC de 16 bits, bytes Programa de 128K de memoria máxima. (Ii) PC ← PC + k + 1 Los dispositivos con PC 22 bits, bytes máximo de 8M de memoria de programa. Sintaxis: Operandos: Contador de Programa: Pila: (I) rcall k-2 K ≤ k <2K PC ← PC + k + 1 PILA ← PC + 1 SP ← SP - 2 (2 bytes, 16 bits) (Ii) rcall k-2 K ≤ k <2K PC ← PC + k + 1 PILA ← PC + 1 SP ← SP - 3 (3 bytes, 22 bits Descripción: Llamada relativa a una dirección dentro PC - 2K + 1 + 2K y PC (las palabras). La dirección de retorno

- 11. (la instrucción después de la rcall) se almacena en la pila. Véase también el LLAMADO. Para AVR microcontroladores con memoria de programa que no exceda de 4 K palabras (8K bytes) esta instrucción puede abordar toda la memoria de todas las ubicaciones de direcciones. El puntero de pila utiliza un esquema de decremento posterior durante rcall. Call - llamada indirecta a la subrutina Operación: (I) PC (15:00) ← Z (15:00) Los dispositivos con PC de 16 bits, el máximo de 128 Kb de memoria de programa. (Ii) PC (15:00) ← Z (15:00) Los dispositivos con PC 22 bits, bytes Programa 8M de memoria máxima. PC (21:16) ← 0 Sintaxis: Operandos: Contador de Programa: Pila: (I) iCall pila de operación ← PC + 1 SP ← SP - 2 (2 bytes, 16 bits) (Ii) iCall pila de operación ← PC + 1 SP ← SP - 3 (3 bytes, 22 bits) Descripción: Llama a una subrutina dentro de la totalidad 4M (palabras) de memoria de programa. La dirección de retorno (a la instrucción después de la llamada) se almacena en la pila. Véase también rcall. El puntero de pila utiliza un esquema de decremento posterior durante la llamada. Esta instrucción no está disponible en todos los dispositivos. Consulte las instrucciones del dispositivo específico EICALL - Convocatoria extendido indirecta a subrutina Operación: (I) PC (15:00) ← Z (15:00) PC (21:16) ← Eind Sintaxis: Operandos: Contador de Programa: Pila: (I) EICALL pila de operación ← PC + 1 SP ← SP - 3 (3 22 bits) Descripción: Llamada indirecta de una subrutina a la que apunta la Z (16 bits) un registro puntero en el Archivo de Registro y el Registro Eind en el espacio de E / S. Esta instrucción permite llamadas indirectas a la totalidad 4M (palabras) el espacio de memoria del programa. Véase también iCall. La Stack Pointer utiliza un esquema de decremento posterior durante EICALL. Esta instrucción no está disponible en todos los dispositivos. Consulte el resumen de un dispositivo específico conjunto de instrucciones. CALL - Convocatoria largo de una subrutina Operación: (i)P PC ← k Devices with 16 bits PC, 128K bytes Program memory maximum.

- 12. (ii) PC ← k Devices with 22 bits PC, 8M bytes Program memory maximum.. Sintaxis: Operandos: Contador de programa: (i) CALL k 0 ≤ k < 64K PC ← kSTACK ← PC+2 SP ← SP-2, (2 bytes, 16 bits) (ii) CALL k 0 ≤ k < 4M PC ← kSTACK ← PC+2 SP ← SP-3 (3 bytes, 22 bits) Descripción: Las llamadas a una subrutina dentro de la memoria del programa entero. La dirección de retorno (a la instrucción después de la llamada) se almacena en la pila. (Véase también rcall). El puntero de pila utiliza un esquema de decremento posterior durante la instrucción CALL.This no está disponible en todos los dispositivos. Consulte el resumen de un dispositivo específico conjunto de instrucciones. RET Subroutine Return PC STACK None 4 / 5 RETI Interrupt Return PC STACK I 4 / 5 CPSE Rd,Rr Compare, Skip if Equal if (Rd = Rr) PC PC + 2 or 3 None 1 / 2 / 3 CP Rd,Rr Compare Rd - Rr Z,C,N,V,S,H 1 CPC Rd,Rr Compare with Carry Rd - Rr - C Z,C,N,V,S,H 1 CPI Rd,K Compare with Immediate Rd - K Z,C,N,V,S,H 1 SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b) = 0) PC PC + 2 or 3 None 1 / SBRS Rr, b Skip if Bit in Register Set if (Rr(b) = 1) PC PC + 2 or 3 None 1 / 2 / 3 SBIC A, b Skip if Bit in I/O Register Cleared if (I/O(A,b) = 0) PC PC + 2 or 3 None SBIS A, b Skip if Bit in I/O Register Set If (I/O(A,b) =1) PC PC + 2 or 3 None 1 / 2 BRBS s, k Branch if Status Flag Set if (SREG(s) = 1) then PC PC + k + 1 None 1 BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PC PC + k + 1 BREQ k Branch if Equal if (Z = 1) then PC PC + k + 1 None 1 / 2 BRNE k Branch if Not Equal if (Z = 0) then PC PC + k + 1 None 1 / 2 BRCS k Branch if Carry Set if (C = 1) then PC PC + k + 1 None 1 / 2 BRCC k Branch if Carry Cleared if (C = 0) then PC PC + k + 1 None 1 / 2 BRSH k Branch if Same or Higher if (C = 0) then PC PC + k + 1 None 1 / 2 BRLO k Branch if Lower if (C = 1) then PC PC + k + 1 None 1 / 2 BRMI k Branch if Minus if (N = 1) then PC PC + k + 1 None 1 / 2 BRPL k Branch if Plus if (N = 0) then PC PC + k + 1 None 1 / 2 BRGE k Branch if Greater or Equal, Signed if (N V= 0) then PC PC + k + 1 BRLT k Branch if Less Than, Signed if (N V= 1) then PC PC + k + 1 None 1 / 2 BRHS k Branch if Half Carry Flag Set if (H = 1) then PC PC + k + 1 None 1 / 2 BRHC k Branch if Half Carry Flag Cleared if (H = 0) then PC PC + k + 1 None 1 BRTS k Branch if T Flag Set if (T = 1) then PC PC + k + 1 None 1 / 2 BRTC k Branch if T Flag Cleared if (T = 0) then PC PC + k + 1 None 1 / 2 BRVS k Branch if Overflow Flag is Set if (V = 1) then PC PC + k + 1 None 1 / 2 BRVC k Branch if Overflow Flag is Cleared if (V = 0) then PC PC + k + 1 None 1 BRIE k Branch if Interrupt Enabled if (I = 1) then PC PC + k + 1 None 1 / 2 BRID k Branch if Interrupt Disabled if (I = 0) then PC PC + k + 1 None 1 / 2

- 13. MOV Rd, Rr Copy Register Rd Rr None 1 MOVW Rd, Rr Copy Register Pair Rd+1:Rd Rr+1:Rr None 1 LDI Rd, K Load Immediate Rd KNone1 LDS