pi-fp-info

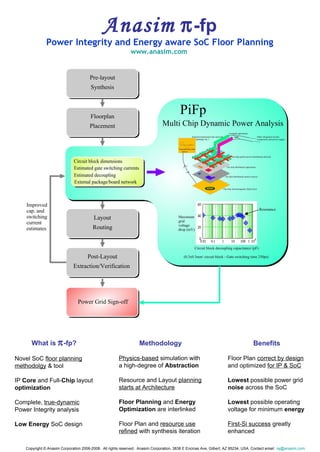

- 1. Anasim p-fp Power Integrity and Energy aware SoC Floor Planning www.anasim.com Methodology Physics-based simulation with a high-degree of Abstraction Resource and Layout planning starts at Architecture Floor Planning and Energy Optimization are interlinked Floor Plan and resource use refined with synthesis iteration Benefits Floor Plan correct by design and optimized for IP & SoC Lowest possible power grid noise across the SoC Lowest possible operating voltage for minimum energy First-Si success greatly enhanced What is p-fp? Novel SoC floor planning methodolgy & tool IP Core and Full-Chip layout optimization Complete, true-dynamic Power Integrity analysis Low Energy SoC design Copyright © Anasim Corporation 2006-2008. All rights reserved. Anasim Corporation, 3838 E Encinas Ave, Gilbert, AZ 85234, USA. Contact email: raj@anasim.com

- 2. Anasim p-fp Power Integrity and Energy aware SoC Floor Planning www.anasim.com A: Analysis run on a floor plan B: Spatial Noise Distribution (dynamic) Methodology Differential, optimized power grid design minimizes effort Simple Netlist input/ GUI, ECD based 10x faster simulator Ease of dynamic results views E: Noise Shaping Noise (mv) Benefits 300 250 200 150 100 50 Rapid ‘what-if’ analyses and resource optimization Accurate, true-dynamic view of core, chip & system noise Low Voltage & Energy SoC D: SIM Simplification Why p-fp? Only tool enhancing static I*R drop with distributed I*R, L*di/dt, and C*dv/dt Only noise propagation tool Only tool revealing 2-D grid, system resonances C: Multi chip/core floor plan capture Simulation netlist .TRAN 200e-12 .PLOT 20 .ACC 0.0060 .PRINTNODE ALL Ggrid1 0.2 0.2 0.0005 0.0080 0.030 10e-9 10e-9 Igrid1 0.1 0.1 0.02 0.02 pulse.txt 1 Ttline1 1 2 0.01 10e-9 100e-12 0.3 Ngrid1 1 0.11 0.11 pulse.txt : Current Source 0 0 22E-12 0.030901699 40E-12 0.058778525 60E-12 0.080901699 80E-12 0.095105652 100E-12 0.1 120E-12 0.095105652 140E-12 0.080901699 160E-12 0.058778525 180E-12 0.030901699 200E-12 0 Maximum noise with grid wire width, 3nf cap 0 5 10 20 30 40 50 Wire width (microns) F: Resource Optimization Copyright © Anasim Corporation 2006-2008. All rights reserved. Anasim Corporation, 3838 E Encinas Ave, Gilbert, AZ 85234, USA. Contact email: raj@anasim.com