MIXED MODE SIMULATION OF HIGH SPEED BOARDS USING DWS

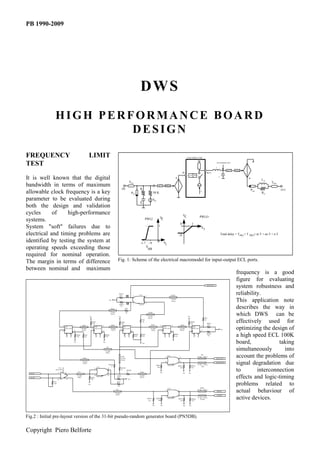

- 1. PB 1990-2009 DWS HIGH PERFORMANCE BOARD DESIGN FREQUENCY LIMIT LOGIC/TIMING CORE TEST OUT SHAPING NET L no T PWLO IN OUT nT TH It is well known that the digital + C + LO TPKI TPKO bandwidth in terms of maximum ni T PWLI IN R P RO OUT allowable clock frequency is a key PRI 50 K I RO parameter to be evaluated during VRI C both the design and validation cycles of high-performance VC V PWLO systems. PWLI C 0 1 System "soft" failures due to 1 VI electrical and timing problems are -.8 Total delay = T PKI + T PKO+ ni T + no T + n T identified by testing the system at -1.7 -.9 0 VI operating speeds exceeding those V BB required for nominal operation. The margin in terms of difference Fig. 1: Scheme of the electrical macromodel for input-output ECL ports. between nominal and maximum frequency is a good figure for evaluating DATA OUT system robustness and RPD13 430 40 2 U5A 4 TXOR2 reliability. Vee 30 3 5 75 ohm 300 ps This application note RPD14 100107 TDAT 430 RS3 describes the way in Vee 75 ohm 300 ps Vee 68 TXOR1 75 ohm 300 ps Vee RS2 which DWS can be RPD3 430 RPD5 430 RS1 68 TINT3 TINT4 RPD10 430 68 RPD11 430 effectively used for 6 7 TINT1 11 TINT2 7 24 11 11 5 U2C 100131FP 8 75 ohm 100 ps 1 U2B 24 100131FP 12 75 ohm 200 ps 5 U3C 6 100131FP 8 75 ohm 100 ps 1 U3B 100131FP 12 75 ohm 200 ps U4B 24 100131FP 12 Vee optimizing the design of 1 4 3 RPD4 330 RS4 68 2 RPD6 330 4 3 RPD8 430 RPD7 430 RPD9 330 2 RPD12 330 a high speed ECL 100K Vee Vee Vee board, taking TD 75 ohm 300 ps simultaneously into TCK1 TCK2 75 ohm 17 U6A 15 TD1 75 ohm 100 ps DATA OUT account the problems of 200 ps 75 ohm 200 ps RSCK1 47 RPD21 18 100102FP RPD15 16 RPD16 75 ohm 100 ps TD2 DATA OUT* signal degradation due U1A 10K 330 330 RSCK2 to interconnection U7A 15 17 100114FP 47 RSCK3 TC1 47 TCK3 Vee 17 16 Vee Vee CK IN CK IN* 18 15 75 ohm 100ps RPD9 330 18 100102FP 16 RPD2 330 Vee 75 ohm 200 ps effects and logic-timing RT1 100 Vee RPD1 330 problems related to U1D TCK01 TC2 75 ohm 100 ps 1 7 75 ohm 100 ps CKOUT actual behaviour of CKOUT* RPD19 330 RPD20 10K 2 100102FP 8 RPD17 330 RPD18 330 75 ohm 100 ps TCK02 active devices. Vee Vee Vee Vee Fig.2 : Initial pre-layout version of the 31-bit pseudo-random generator board (PN5DB). Copyright Piero Belforte

- 2. HIGH SPEED BOARD -2 V MODEL RT ERM PN50PT 75 300 100 100K logic gates and flip-flops are 400 Data (U2A) CK (U2A) DAT A_OUT 200 DAT A_OUT accurately modelled at electrical- 500 timing-logic levels, including such CK_IN 600 key issues as timing skew between CK_IN T cable1 T cable2 reset set outputs, internal path delay 50 ohm 50 ohm 2 ns 2 ns mismatches and input-output ideal cable ideal cable electrical equivalents obtained by 501 601 taking into account package and R 50 R 50 nonlinear effects as observed in VCP1 VCP2 device characterization (Fig. 1). In V3 this particular case, an equivalent VCH 1.3 volt V2 V reset V set 2 ns pulse 1.7 volt electrical model for input-output SWGEN ports is used instead of the more direct s-parameter behavioural Fig. 3: Electrical scheme of the test set-up used to evaluate the limit frequency of the PRBS board. model used for other applications. -0.50 V Despite the complexity of the resulting model network (on the -1.30 V V(100) layout4.g order of a thousand elements) and -2.00 V -0.50 V * 245 MHz the number of calculated time- points necessary to achieve a good -1.30 V V(100) layout3.g resolution (on the order of several -2.00 V -0.50 V * 239 MHz thousand), DWS runs require few milliseconds on a standard PC -1.30 V V(100) layout2.g , so that the interactive * 235 MHz -2.00 V -0.50 V optimization recycles are -1.30 V accomplished in a small amount of V(100) * frequency limit layout1.g time. -2.00 V * 218 MHz -0.50 V -1.30 V V(400) DESIGN OPTIMIZATION layout1.g -2.00 V 0.50 0.55 0.60 0.65 0.70 0.75 0.80 0.85 0.90 0.95 1.00 Starting with an initial pre-layout TIME[uS] version of the pseudo-random Fig. 4a: Layout impact on performance: swept freq. test (200-250 MHz) generator board (PN5DB) -0.50 V including interconnects impedance and length evaluation (Fig. 2), -1.30 V V(200) layout4.g DWS simulation easily pinpoint -2.00 V -0.50 V the causes of failures when * 245 MHz working at higher clock -1.30 V V(200) layout3.g frequencies. To achieve this goal a -2.00 V -0.50 V limit frequency test setup is * 239 MHz simulated as shown in Fig.3. -1.30 V V(200) layout2.g The board is connected to a sweep -2.00 V -0.50 V * 235 MHz frequency clock generator and the most significant board signals are -1.30 V V(200) layout1.g monitored in order to observe -2.00 V -0.50 V * 218 MHz when a failure occurs. -1.30 V Typical failures consist of an V(400) layout1.g incorrect bit sequence with respect -2.00 V to a pseudo-random 31-bit 0.50 0.55 0.60 0.65 0.70 0.75 0.80 0.85 0.90 0.95 1.00 TIME[uS] Fig. 4b: Layout impact on performance: swept freq. test (200-250 MHz) 2 Copyright Piero Belforte

- 3. sequence expected during correct overshoots due to reflections violation on the first 100131 D- type master-slave flip-flop (U2A) causing detestable operation. LAYOUT VERSION After this first result several design modifications have been evaluated #1 #2 #3 # 4 (opt) in order to identify the best TCK1 300 200 200 200 solution and the impact on TRACE performance is summarized in Fig. ELECTRICAL TCK2 100 200 200 200 5. The most relevant improvement in terms of clock speed is obtained LENGTH TCK3 100 200 200 200 by shortening the delay of input- ( ps ) output traces of the exclusive-or TDAT 300 300 200 100 gate U5A (100107) from 300ps (~ 6cm) to 100ps (~ 2cm) and trying F max. sweep 218 235 239 245 to increase the delay of the clock path of U2A with respect the ( MHz ) other flip-flops in the chain. This fixed - - - 238.1 last adjustment is implemented Fig. 5: Summary of the limit frequency versus layout parameters: trace length has great utilizing the clock driver gate impact on performance U1A (100102) as delay for U2A and U2B clock inputs and operation (Fig. 4). within device package, output trace connecting the other flip-flops -2 V RPD7 RPD11 RPD13 75 75 U5D TXOR2 430 7 1 Vee 75 ohm TDAT 100 ps 75 ohm 6 24 100107FP 100 ps TXOR1 Vee Vee 75 ohm Vee 300 ps 300 RPD3 RPD5 RPD10 U2A 430 430 430 RPD14 100131FP TINT3 TINT4 15 14 TINT1 11 TINT2 7 24 11 11 -2 V U2B U3C U3B U4B 16 24 100131FP 75 ohm 6 100131FP 100131FP 75 ohm 24 100131FP 75 75 ohm 75 ohm 100 ps 200 ps 100 ps 200 ps RPD12 20 13 12 8 12 12 1 5 1 400 1 Vee RPD9 330 RPD4 RS4 RPD6 4 3 RPD8 4 3 2 2 2 330 330 430 330 68 Vee Vee Vee TCK2 75 ohm 200 ps TCK3 75 ohm 200 ps TD1 U6A TD 17 15 75 ohm 100 ps 100 DATA OUT TCK1 75 ohm 300 ps 18 16 DATA OUT 75 ohm 75 ohm 100 ps 200 200 ps RPD21 100102FP RPD15 Vee TD2 10K 330 RPD22 RSCK1 10K 47 Vee Vee U1A U7D 15 17 TCIN1 100114FP 500 50 ohm 200 ps TC1 1 8 CK IN 75 ohm 18 16 100102FP CK IN 100ps RPD9 330 600 2 7 330 Vee 50 ohm 200 ps TCIN2 RT1 RPD1 100 -2 V 330 TCK01 U1D TC2 1 7 75 ohm 100 ps CKOUT 75 ohm 100 ps CKOUT 2 8 75 ohm 100 ps RPD19 RPD20 100102FP RPD17 RPD18 TCK02 330 10K 330 330 Vee Vee Vee Vee Fig. 6: Optimized version of the 31-bit pseudo-random generator board (PN50PT) The behaviour differences and connector, while output 100, directly to the output of the between output data signals being left open for bus differential line receiver U7A V(200) and V(100) are applications, has a more (100114) (Fig.6). Minor speed caused by straightforward behaviour because improvements are also obtained by different termination schemes: it is terminated off the board modifying the type of terminations complementary output 200 has a (RTERM visible on Fig. 3). used on critical paths turning series pull down load within the board The limit frequency for the initial into parallel arrangements. and no termination resistor, so that design turns out to be about the waveform is affected by strong 200 MHz due to setup time 3 Copyright Piero Belforte

- 4. RESULTS The final result is the PN5OPT pre-layout version which operates correctly up to about 238 MHz in the fixed frequency test and up to 245 MHz in the swept frequency set-up showing a 20% performance improvement over the initial design. This result is obtained with board implementations utilizing active devices packaged in flat-packs. It is interesting to evaluate the impact on performance due to -0.50 V * FP packaging effects: substituting larger 24-pin devices for the -1.30 V original flat-packs, while leaving V(100) layout4.g pcb trace lengths unchanged, * 245 MHz causes a decrease in maximum -2.00 V -0.50 V operating frequency (sweep test) * DIL from 245 MHz to 229 MHz showing the great importance of -1.30 V V(100) pn5db8dil.g packaging issues for this kind of * 229 MHz design (Fig. 7). An analysis -2.00 V -0.50 V procedure similar to that previously shown can be applied after the board layout definition in -1.30 V V(400) pn5db8dil.g order to verify the way in which the differences in the -2.00 V interconnection paths (length, 0.50 0.55 0.60 0.65 0.70 0.75 0.80 0.85 0.90 0.95 1.00 impedance, via holes, trace TIME[uS] proximity, etc.) can affect the Fig. 7: Maximum operating frequency (sweep test) comparison between flat and 24 pin dual-in-line package. performance with respect to the pre-layout specification. 4 Copyright Piero Belforte