Bab 4 register

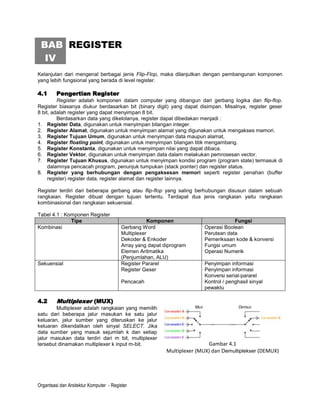

- 1. BAB REGISTER IV Kelanjutan dari mengenal berbagai jenis Flip-Flop, maka dilanjutkan dengan pembangunan komponen yang lebih fungsional yang berada di level register. 4.1 Pengertian Register Register adalah komponen dalam computer yang dibangun dari gerbang logika dan flip-flop. Register biasanya diukur berdasarkan bit (binary digit) yang dapat disimpan. Misalnya, register geser 8 bit, adalah register yang dapat menyimpan 8 bit. Berdasarkan data yang dikelolanya, register dapat dibedakan menjadi : 1. Register Data, digunakan untuk menyimpan bilangan integer. 2. Register Alamat, digunakan untuk menyimpan alamat yang digunakan untuk mengakses memori. 3. Register Tujuan Umum, digunakan untuk menyimpan data maupun alamat, 4. Register floating point, digunakan untuk menyimpan bilangan titik mengambang. 5. Register Konstanta, digunakan untuk menyimpan nilai yang dapat dibaca. 6. Register Vektor, digunakan untuk menyimpan data dalam melakukan pemrosesan vector. 7. Register Tujuan Khusus, digunakan untuk menyimpan kondisi program (program state) termasuk di dalamnya pencacah program, penunjuk tumpukan (stack pointer) dan register status. 8. Register yang berhubungan dengan pengaksesan memori seperti register penahan (buffer register) register data, register alamat dan register lainnya. Register terdiri dari beberapa gerbang atau flip-flop yang saling berhubungan disusun dalam sebuah rangkaian. Register dibuat dengan tujuan tertentu. Terdapat dua jenis rangkaian yaitu rangkaian kombinasional dan rangkaian sekuensial. Tabel 4.1 : Komponen Register Tipe Komponen Fungsi Kombinasi Gerbang Word Operasi Boolean Multiplexer Perutean data Dekoder & Enkoder Pemeriksaan kode & konversi Array yang dapat diprogram Fungsi umum Elemen Aritmatika Operasi Numerik (Penjumlahan, ALU) Sekuensial Register Pararel Penyimpan informasi Register Geser Penyimpan informasi Konversi serial-pararel Pencacah Kontrol / penghasil sinyal pewaktu 4.2 Multiplexer (MUX) Multiplexer adalah rangkaian yang memilih satu dari beberapa jalur masukan ke satu jalur keluaran, jalur sumber yang diteruskan ke jalur keluaran dikendalikan oleh sinyal SELECT. Jika data sumber yang masuk sejumlah k dan setiap jalur masukan data terdiri dari m bit, multiplexer tersebut dinamakan multiplexer k input m-bit. Gambar 4.1 Multiplexer (MUX) dan Demultiplekser (DEMUX) Organtsasi dan Arsitektur Komputer - Register

- 2. Pengertian bebas dari Multiplexer adalah alat atau komponen elektronika yang bisa memilih input (masukan) yang akan diteruskan ke bagian output (keluaran). Pemilihan input mana yang dipilih akan ditentukan oleh signal yang ada di bagian kontrol (kendali) SELECT. Komponen yang berfungsi kebalikan dari MUX ini disebut Demultiplekser (DEMUX). Pada DEMUX, jumlah masukannya hanya satu, tetapi bagian keluarannya banyak. Signal pada bagian input ini akan disalurkan ke bagian output (channel) yang mana tergantung dari kendali pada bagian SELECT-nya. Simbol In 0 In 1 In 2 In -1 Simbol multiplexer terdiri dari k buah input dan masing-masing m m m m memiliki m-bit, s buah SELECT, satu buah ENABLE e dan 1 buah m bit keluaran. Jumlah masukan k menentukan berapa jumlah SELECT SELECT 2 yang diperlukan. Jumlah SELECT > Log k. Misalkan ai = 1 jika Multiplexer (MUX) input i yang dipilih. Jika ai = 1 ketika bilangan biner i ditetapkan pada jalur SELECT, maka In i akan dihubungkan dengan Out jika ENABLE e e = 1. Jalur ENABLE e adalah jalur untuk mengaktifkan m Multiplexer. Jika e bernilai 0 maka Multiplexer tidak aktif. Operasi Multiplexer dapat didefinisikan secara formal dengan persamaan Out Boolean m-SOP sebagai berikut : Gambar 4.2 Multiplexer k-input m-bit Out j = i, j ai e untuk j = 0, 1, 2,…, m-1 In 1,3 Multiplexer mempunyai properti penting yang dapat digunakan untuk Out 3 menghasilkan berbagai fungsi In 0,3 kombinasional dan dapat digambarkan sebagai diagram logika yang universal. In 1,2 Spesifiknya pada n-variabel fungsi Out dapat dibuat oleh Multiplexer 2n-input 1-bit. Out 2 Hal ini dapat dilakukan dengan s jalur In 0,2 control SELECT. Jika In i (In0, In1, In2,…In n-1) dengan s jalur kontrol SELECT. Jika In i menyatakan jalur input data ke-I, maka In 1,1 output Out. Dari Gambar 4.3, Multiplexer Out 1 tersebut terdiri dari 2 input yaitu In 0 dan In In 0,1 1 yang masing-masing terdiri dari 4 bit. Karena terdapat 2 buah masukan maka In 1,0 SELECT yang diperlukan sebanyak 2 2 Log In = Log 2 = 1. SELECT dapat bernilai Out 0 0 untuk memilih In 0 dan dapat bernilai 1 In 0,0 untuk memilih In 1. EN SELECT Gambar 4.3 Diagram Logika Multiplexer 2-input 4-bit Organtsasi dan Arsitektur Komputer - Register

- 3. Registers Z 0 ALU R MUX Sign 1 Extend Gambar 4.4 Simbol Dekoder 1/n Rangkaian Multiplexer biasanya digunakan untuk menggabungkan dua atau lebih sinyal digital ke dalam satu jalur, dengan menempatkan pada waktu yang berbeda. Cara seperti ini dikenal dengan istilah multipleks berdasarkan pembagian waktu (Time Division Multiplexing). Multiplexer banyak digunakan dalam computer, salah satu implementasinya adalah pada saat memilih satu masukan dari beberapa masukan sumber untuk ALU (Arithmetic and logical unit). 4.3 Decoder Aplikasi utama decoder adalah pengalamatan, dimana n bit masukan In diinterprestasikan sebagai sebuah alamat yang digunakan untuk memilih satu dari jalur keluaran. Aplikasi yang lain adalah member rute data dari sebuah sumber ke beberapa tujuan. Dekoder juga disebut demultiplexer. Aplikasi ini dapat mengendalikan input dari decoder yang dipandang sebagai 1 bit data sumber. Out 7 Out 6 Out 5 In 2 Out 4 In 1 In 0 Out 3 Out 2 Out 1 Out 0 EN Gambar 4.5 Diagram Logika Dekoder 1/8 Organtsasi dan Arsitektur Komputer - Register

- 4. n n Sebuah decoder 1-out-of-2 atau 1/2 adalah rangkaian kombinasional dengan n jalur data masukan dan 2n jalur data keluaran. Sinyal keluaran yang aktif tergantung dari nilai masukan In 0, In 1, In 2. Berikut ini daftar kombinasi sinyal masukan dan efek sinyal keluaran yang aktif; Tabel 4.2 Tabel Kebenaran pada Diagram Logika Decoder 1/8 Sinyal Masukan Keluaran In 0 In 1 In 2 EN Aktif 0 0 0 1 Out 0 0 0 1 1 Out 1 0 1 0 1 Out 2 0 1 1 1 Out 3 1 0 0 1 Out 4 1 0 1 1 Out 5 1 1 0 1 Out 6 1 1 1 1 Out 7 Φ Φ Φ 0 Tidak Ada Kombinasi sinyal masukan akan menentukan sinyal keluaran yang aktif. Chip decoder dikendalikan oleh chip ENABLE (EN). Pada saat nilai ENABLE (EN) rendah maka decoder tidak berfungsi, apapun kombinasi masukannya. Bila diperhatikan, jalur keluaran yang aktif ditentukan oleh nilai kombinasi IN. Pada saat In 0 In 1 In 2 = 001 maka keluaran yang aktif adalah Out 1. In 0 In 1 In k k > 2Log n. ……. Dekoder 1/n EN ……. Out 0 Out 1 Out n Gambar 4.5 Penggunaan MUX dalam Prosesor MIPS Simbol decoder terdiri dari k buah masukan, sebuah jalur ENABLE (EN), dan n buah jalur 2 keluaran dengan syarat k > Log n. Misal jumlah keluarannya 8 jalur maka k minimal sama dengan 2 Log 8 = 3. 4.4 Encoder Encoder adalah rangkaian yang digunakan untuk menghasilkan alamat atau nama dari jalur masukan yang aktif. Encoder kebalikan dari decoder. Penambahan In Aktif digunakan untuk mengetahui apakah ada atau tidah sebuah jalur yang aktif. Pada saat tidak ada jalur yang aktif, keluaran akan bernilai 00, ini akan sama artinya dengan jalur In 0 yang aktif. Keluaran In Aktif dibuat untuk membedakan antara tidak ada masukan yang aktif dengan masukan In 0 yang aktif. Gambar 4.5 di bawah ini menunjukkan sebuah 4 bit encoder yang sederhana untuk tipe ini. Organtsasi dan Arsitektur Komputer - Register

- 5. Out 1 In 3 In 2 In 1 In 0 Out 0 In AKTIF EN Gambar 4.6 Diagram Logika Encoder 4 Bit Simbol In Simbol encoder n bit terdiri dari n bit masukan In, 2 n satu buah ENABLE (EN) dan In Aktif, serta Log n bit keluaran. EN Encoder In AKTIF N bit 2 Log n Out Gambar 4.7 Simbol Encoder N Bit 4.5 Register Data In 3 D Set Q Out 3 Register data adalah kumpulan elemen-elemen CK FF memori yang bekerja bersama-sama sebagai satu unit. Q’ Fungsinya sebagai penyimpan data. CLR In Set In 2 D Q Out 2 CK FF n Q’ CLR Detak In 1 D Set Q Out 1 Register Data N bit CK FF CLR Q’ CLR n Set In 0 D Q Out 0 N CK FF Q’ Gambar 4.9 Simbol Register Data N bit CLR DETAK CLEAR Gambar 4.8 Rangkaian Register Data N bit Organtsasi dan Arsitektur Komputer - Register

- 6. Sumber m bit register dirangkai dengan m flip-flop digunakan untuk menyimpan sebuah m bit word (In 0, In 1, …In m-1). Setiap bit word disimpan dalam flip flop yang berlainan. Data dapat dikirim kea tau dari semua flip flop secara bersamaan, mode operasi ini disebut masukan-keluaran pararel (pararel input-output). Register data dapat dibangun dari berbagai tipe flip flop. Simbol register data terdiri dari n bit In, jalur DETAK dan CLEAR, dan n bit OUT. 4.6 Register Geser Terdapat berbagai situasi dalam perancangan computer di mana diperlukan adanya pergeseran isi register ke sebelah kiri atau sebelah kanan. Operasi pergeseran kanan mengubah keadaan register sebagai berikut : (0, Z0, Z1, …, Zm-1) (Z0, Z1, … Zm-1) Dan pergesaran kiri melakukan transformasi : ( Z1, Z2…, Zm-1, 0) (Z0, Z1, … Zm-1) Register yang dapat melakukan operasi penggeseran ke kiri atau ke kanan ini disebut dengan register geser (shift register). Untuk melaksanakan operasi sederhana ini. Register geser m-bit terdiri dari m buah flip flop master-slave yang masing-masingnya dihubungkan dengan tetangga sebelah kiri dan kanannya. Data satu bit dapat dimasukkan dan satu bit dapat dibaca pada sisi yang lain. Ini disebut input-output parallel. Simbol register geser n bit terdiri dari jalur in, SHEN, CLEAR, dan OUT. Set Set Set Set IN D Q D Q D Q D Q OUT CK FF CK FF CK FF CK FF Q’ Q’ Q’ Q’ CLR CLR CLR CLR SHEN CLEAR Gambar 4.10 Register Geser Pergeseran ke kanan dapat dikerjakan dengan In mengaktifkan jalur kendali shift enable yang n terhubung dengan input CLOCK masing-masing flip flop. Berguna juga untuk menyediakan akses langsung pada flip flop internal dalam register SHEN Register Geser geser m-bit. Disamping jalur data serial, m jalur N bit input atau output disediakan juga untuk transfer CLR data parallel dari dank e register geser. Register geser sangat berguna pada n sejumlah aplikasi seperti : Out 1. Penyimpanan data serial Gambar 4.11 Simbol Register Geser n bit 2. Konversi data serial ke parallel atau parallel ke serial 3. Melakukan operasi aritmatik Register geser dapat dirancang agar lebih universal yang menggabungkan register geser kanan atau kiri. Berikut ini gambar register geser universal. Organtsasi dan Arsitektur Komputer - Register

- 7. Data IN Data IN Data IN Geser Kanan Parallel Geser Kiri n n n PAR EN LEFT SH Register Geser SHEN N bit CLR n n n Data OUT Data OUT Data OUT Geser Kiri Parallel Geser Kanan Gambar 4.12 Simbol Register Geser Kanan-Kiri n bit 4.7 Pencacah (Counter) Pencacah adalah sebuah mesin sekuensial yang dirancang untuk melakukan pencacahan. Pencacah sederhana diperoleh dengan sedikit melakukan modifikasi dari register geser. Gambar 4.13 menunjukkan pencacah modulo-16 yang dapat mencacah dari 0000 sampai 1111. Pencacah ini terdiri dari 4 buah JK flip flop. 1 Set Set Set Set J Q J Q J Q J Q COUNTEN CK FF CK FF CK FF CK FF K Q’ K Q’ K Q’ K Q’ CLR CLR CLR CLR CLEAR OUT 0 OUT 1 OUT 2 OUT 3 Gambar 4.13 Diagram Logika Pencacah Modulo-16 (Ripple Counter) Rangkaian ini akan menghitung jika jalur Count aktif. Keluaran hasil penghitungan adalah 4 bit standar bilangan biner. Keluaran suatu flip flop merupakan masukan bagi flip flop di sebelah kanannya sehingga keluaran dari suatu flip flop akan mempengaruhi keadaan flip flop yang ada di sebelah kanannya. Tipe pencacah seperti ini disebut ripple counter. Jalur COUNTEN berfungsi sebagai pengganti detak bagi JK flip flop pertama. Jalur CLEAR berfungsi untuk me-RESET (mengosongkan) nilai seluruh JK flip flop. Konstanta 1 berfungsi member nilai 1 pada masukan J dan K untuk semua flip flop. Karena JK senantiasa bernilai 11 maka flip flop dalam kondisi toggle (berubah-ubah dari kondisi sebelumnya) Simbol Simbol pencacah modulo-16 terdiri dari 4 bit keluaran, 1 bit jalur COUNTEN dan CLEAR. COUNTEN PENCACAH MODULO-16 CLEAR Out 0 Out 1 Out 2 Out 3 Gambar 4.14 Simbol Pencacah Modulo-16 Organtsasi dan Arsitektur Komputer - Register