Chuong 3 khao sat tap lenh va ltrinh vdk

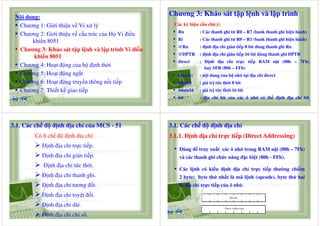

- 1. Nội dung: Chương 3: Khảo sát tập lệnh và lập trình • Chương 1: Giới thiệu về Vi xử lý Các ký hiệu cần chú ý: • Chương 2: Giới thiệu về cấu trúc của Họ Vi điều • Rn : Các thanh ghi từ R0 – R7 (bank thanh ghi hiện hành) khiển 8051 • Ri : Các thanh ghi từ R0 – R1 (bank thanh ghi hiện hành) • @Rn : định địa chỉ gián tiếp 8 bit dùng thanh ghi Rn • Chương 3: Khảo sát tập lệnh và lập trình Vi điều khiển 8051 • @DPTR : định địa chỉ gián tiếp 16 bit dùng thanh ghi DPTR • direct : Định địa chỉ trực tiếp RAM nội (00h – 7Fh) • Chương 4: Hoạt động của bộ định thời hay SFR (80h – FFh) • Chương 5: Hoạt động ngắt • (direct) : nội dung của bộ nhớ tại địa chỉ direct • Chương 6: Hoạt động truyền thông nối tiếp • #data8 : giá trị tức thời 8 bit • Chương 7: Thiết kế giao tiếp • #data16 : giá trị tức thời 16 bit • bit : địa chỉ bit của các ô nhớ có thể định địa chỉ bit 3.1. Các chế độ định địa chỉ của MCS - 51 3.1. Các chế độ định địa chỉ Có 8 chế độ định địa chỉ: 3.1.1. Định địa chỉ trực tiếp (Direct Addressing) Định địa chỉ trực tiếp. • Dùng để truy xuất các ô nhớ trong RAM nội (00h – 7Fh) Định địa chỉ gián tiếp. và các thanh ghi chức năng đặc biệt (80h - FFh). Định địa chỉ tức thời. • Các lệnh có kiểu định địa chỉ trực tiếp thường chiếm Định địa chỉ thanh ghi. 2 byte: byte thứ nhất là mã lệnh (opcode), byte thứ hai Định địa chỉ tương đối. là địa chỉ trực tiếp của ô nhớ. Định địa chỉ tuyệt đối. Định địa chỉ dài. Định địa chỉ chỉ số.

- 2. 3.1. Các chế độ định địa chỉ 3.1. Các chế độ định địa chỉ 3.1.1. Định địa chỉ trực tiếp (Direct Addressing) 3.1.2. Định địa chỉ gián tiếp (Indirect Addressing) Ví dụ: Các lệnh sau có kiểu định địa chỉ trực tiếp: Dùng để truy xuất cho cả RAM nội và RAM ngoài. MOV A, P0 • Các thanh ghi R0 và R1 hoạt động như các con trỏ, dùng ⇒ Chuyển nội dung từ Port 0 vào thanh ghi A để truy xuất RAM nội. Nội dung của các thanh ghi này là MOV A, 30h địa chỉ của RAM nội. ⇒ Chuyển nội dung của ô nhớ có địa chỉ 30h vào Ví dụ: MOV A, @R0 thanh ghi A ⇒ Chuyển nội dung của RAM nội có địa chỉ chứa trong R0 vào thanh chứa A. 3.1. Các chế độ định địa chỉ 3.1. Các chế độ định địa chỉ 3.1.2. Định địa chỉ gián tiếp (Indirect Addressing) 3.1.3. Định địa chỉ tức thời (Immediate Addressing) • Thanh ghi DPTR dùng để truy xuất RAM ngoại • Dùng để đưa trực tiếp hằng số vào mã lệnh của chương Ví dụ: MOV DPTR, #5000h trình. Hằng số được xác định bằng cách sử dụng dấu #. MOVX A, @DPTR Ví dụ: MOV A, #10h; ⇒ Nạp giá trị 10h vào thanh chứa A. ⇒Nạp địa chỉ 5000h (RAM ngoài) vào con trỏ DPTR; ⇒ Chuyển nội dung của RAM ngoài có địa chỉ chứa trong • Lệnh này chiếm từ 2 đến 3 byte DPTR vào thanh chứa A. • Các lệnh ở chế độ địa chỉ gián tiếp chỉ chiếm 1 byte

- 3. 3.1. Các chế độ định địa chỉ 3.1. Các chế độ định địa chỉ 3.1.4. Định địa chỉ thanh ghi (Register Addressing) 3.1.5. Định địa chỉ tương đối (Relative Addressing) • Dùng cho các lệnh xử lý dữ liệu chứa trong thanh ghi. • Kiểu định địa chỉ này sử dụng cho các lệnh nhảy. Nơi nhảy Việc truy xuất thanh ghi làm việc trong 8 thanh ghi đến có địa chỉ bằng địa chỉ hiện hành trong thanh ghi PC (R0 đến R7) được mã hóa bằng 3 bit trong Opcode. cộng với địa chỉ tương đối (Relative Offset). Ví dụ: ADD A, R2 ⇒ Cộng nội dung của R2 và A MOV R0, A • Địa chỉ tương đối là một số 8 bit có dấu nên tầm nhảy ngắn ⇒ Chuyển nội dung thanh ghi A vào R0 giới hạn từ -127 byte (nhảy lùi) đến 128 byte (nhảy tới). • Mã lệnh thuộc kiểu này chiếm 1 byte Ví dụ: SJMP X1 ⇒ Nhảy đến nhãn có tên X1 nằm trong giới hạn 256 byte 3.1. Các chế độ định địa chỉ 3.1. Các chế độ định địa chỉ 3.1.5. Định địa chỉ tương đối (Relative Addressing) 3.1.6. Định địa chỉ tuyệt đối (Absolute Addressing) Lệnh nhảy thuộc kiểu định địa chỉ này chiếm 2 byte. • Kiểu định địa chỉ này dùng với các lệnh ACALL và AJMP. • Byte thứ nhất là mã lệnh (Opcode). • Các lệnh này chiếm 2 byte. Trong đó, Opcode nằm ở 5 bit • Byte thứ hai là địa chỉ tương đối (Relative Offset). cao. Nơi nhảy đến hoặc gọi đến nằm trong phạm giới hạn 2 kbyte.

- 4. 3.1. Các chế độ định địa chỉ 3.1. Các chế độ định địa chỉ 3.1.6. Định địa chỉ tuyệt đối (Absolute Addressing) 3.1.7. Định địa chỉ dài (Long Addressing) • Kiểu định đại chỉ này dùng với các lệnh LCALL và LJMP. Ví dụ: AJMP X2 • Các lệnh này chiếm 3 byte. Trong đó, 2 byte chứa địa chỉ ⇒ Nhảy đến nhãn có tên X2 nằm trong giới hạn 2 của nơi đến. Do đó, Nơi nhảy đến hoặc gọi đến nằm trong giới hạn 64 kbyte. kbyte 3.1. Các chế độ định địa chỉ 3.1. Các chế độ định địa chỉ 3.1.8. Định địa chỉ chỉ số (Indexed Addressing) 3.1.8. Định địa chỉ chỉ số (Indexed Addressing) • Kiểu định đại chỉ này dùng “một thanh ghi cơ bản (Base Register)” (PC hoặc DPTR) kết hợp với “một • Ví dụ: MOVX A, @A+DPTR giá trị lệch (Offset)” để tạo ra địa chỉ của ô nhớ cần ⇒ Chuyển dữ liệu trong vùng nhớ A + DPTR vào truy xuất hoặc địa chỉ của nơi nhảy đến. thanh chứa A.

- 5. 3.2. Tập lệnh của MCS - 51 3.2. Tập lệnh của MCS - 51 • Tập lệnh của MCS-51 được thiết kế với Opcode 8 bit. Gồm 5 nhóm lệnh cơ bản: ⇒ Có khả năng mã hóa 256 lệnh khác nhau (thực tế có Nhóm lệnh số học (ADD, SUB, MUL, DIV,…). 255 lệnh). • Ngoài Opcode, một lệnh còn có thể có 1 hoặc 2 byte để Nhóm lệnh logic (AND, OR, XOR, NOT,…). mã hóa chế độ địa chỉ: Nhóm lệnh chuyển dữ liệu (MOV). 139 lệnh 1 byte. Nhóm lệnh xử lý bit (SETB, CLR,…). 92 lệnh 2 byte. Nhóm lệnh rẽ nhánh (JMP,…). 24 lệnh 3 byte. 3.2. Tập lệnh của MCS - 51 3.2. Tập lệnh của MCS - 51 3.2.1. Nhóm lệnh số học 3.2.1. Nhóm lệnh số học Gồm các lệnh: Tất cả các lệnh số học được thực thi trong 1 chu kỳ • Cộng: ADD máy (1µs), trừ các lệnh: µ • Trừ: SUBB • INC DPTR ⇒ thực thi trong 2 chu kỳ máy. • Nhân: MUL • Các lệnh MUL, DIV ⇒ thực thi trong 4 chu kỳ • Chia: DIV máy. • Tăng: INC • Giảm: DEC

- 6. 3.2. Tập lệnh của MCS - 51 3.2. Tập lệnh của MCS - 51 3.1.2. Nhóm lệnh logic 3.1.3. Nhóm lệnh di chuyển dữ liệu • Nhóm lệnh logic thực hiện các phép toán logic trên các Nhóm lệnh chuyển dữ liệu bao gồm: byte dữ liệu. Trong đó, thanh chứa A luôn đóng vai trò • Chuyển dữ liệu trong RAM nội: MOV, XCH, XCHD là một toán hạng và lưu kết quả. • Chuyển dữ liệu trong RAM ngoài: MOVX • Tất cả các lệnh logic đều được thực hiện trong 1 chu • Chuyển dữ liệu từ bộ nhớ chương trình: MOVC kỳ máy. (thường dùng để truy xuất bảng dữ liệu trong bộ nhớ • Nhóm lệnh logic bao gồm: ANL, ORL, XRL, CPL, RL chương trình ). (Rotate Left), RR (Rotate Right). • Truy nhập ngăn xếp: PUSH, POP. 3.2. Tập lệnh của MCS - 51 3.2. Tập lệnh của MCS - 51 3.1.4. Nhóm lệnh xử lý bit 3.1.5. Nhóm lệnh rẽ nhánh chương trình Bao gồm các lệnh: Bao gồm các lệnh: • Xóa, thiết lập bit: CLR, SETB • Gọi chương trình con: ACALL, LCALL, RETI • Logic: ANL, ORL, CPL • Nhảy không điều kiện: JMP, SJMP, LJMP, AJMP • Di chuyển bit: MOV • Nhảy có điều kiện: JC, JNC, JB, JNB, JZ, JNZ, CJNE, DJNE

- 7. 3.3. Lập trình hợp ngữ cho MCS - 51 3.3. Lập trình hợp ngữ cho MCS - 51 3.3.1. Trình dịch hợp ngữ 3.3.2. Khuôn dạng của chương trình hợp ngữ • Khi chương trình nguồn được viết, phần mở rộng của tập tin nguồn là “.asm” hoặc “.src”. Lệnh trong hợp ngữ có 4 trường như sau: • Trình dịch hợp ngữ của 8051 sẽ dịch tập tin này ra dạng mã [Nhãn:] [Từ gợi nhớ] [Các toán hạng] [;Chú thích] máy và tạo ra tập tin đối tượng (.obj) và tập tin liệt kê (.lst). • Các chương trình 8051IDE, Keil C51 là các chương trình Ví dụ: bao gồm 3 chức năng: soạn thảo chương trình nguồn, dịch Loop: MOV A, P0 ; Chuyển(P0)→(A) → chương trình nguồn và mô phỏng được ứng dụng khi lập trình MCS – 51. Chương trình thực hiện như sau: 3.3.2. Khuôn dạng của chương trình hợp ngữ ORG 0000H ; Địa chỉ bắt đầu Không nhất thiết lúc nào cũng có đầy đủ 4 trường, Tuy MOV TMOD, #10h ; Thiết lập chế độ 1 của Timer 1 nhiên, có một số điểm cần lưu ý: Loop: MOV TH1, #HIGH (-500) ; Nạp byte cao của -500 MOV TL1, #LOW (-500) ; Nạp byte thấp của -500 • Nhãn: cho phép chương trình tham chiếu đến một dòng SETB TR1 ; Cho phép timer 0 hoạt động lệnh bằng tên nhãn. Wait: JNB TF1, Wait ; Nếu Timer chưa tràn thì chờ CLR TF1 ; Xóa cờ tràn • Từ gợi nhớ và toán hạng: kết hợp với nhau để thực hiện CPL P1.0 ; Đảo bit P1.0 để tạo xung vuông nhiệm vụ của chương trình. CLR TR1 • Chú thích: ghi vào các lời giải thích cho chương trình và SJMP Loop được viết sau dấu “;”. Trình dịch hợp ngữ sẽ bỏ qua các END chú thích này khi dịch chương trình.

- 8. 3.3.3. Các chỉ dẫn 3.3.3. Các chỉ dẫn Chỉ dẫn ORG (Set origin): Chỉ dẫn END Dùng để khai báo địa chỉ bắt đầu của chương trình. • Chỉ dẫn này báo cho trình dịch hợp ngữ biết kết ORG Expression thúc tập tin nguồn (.ASM). Expression: địa chỉ bắt đầu của chương trình tronng bộ nhớ chương trình. • Chỉ dẫn END là dòng cuối cùng của chương trình Ví dụ: ORG 300h 8051, nghĩa là mọi lệnh sau END đều bị trình dịch Các lệnh …,,,,,, bỏ qua. ⇒ Chương trình bắt đầu từ địa chỉ 300h trong ROM 3.3.3. Các chỉ dẫn 3.3.3. Các chỉ dẫn Chỉ dẫn EQU (Equate) Chỉ dẫn DB (Define Byte) • Chỉ dẫn dùng để định nghĩa (các) giá trị byte dữ liệu. • Chỉ dẫn này được dùng để gán (định nghĩa) một Thường được dùng để đặt các hằng số (bảng dữ liệu) vào giá trị cho nhãn. bộ nhớ chương trình. [Label:] DB Expression Symbol EQU Expression Ví dụ: ORG 500h • Ví dụ: Led7 EQU P0 DATA: DB 12h, 55h, 64h, 08h…. MOV Led7, A ;Xuất dữ liệu từ A ⇒ P0 ⇒ Định nghĩa DATA gồm các giá trị: 12h, 55h, 64h, Count EQU 100 ;Count có giá trị 100 ….nằm trong bộ nhớ ROM với địa chỉ bắt đầu 500h

- 9. 3.3.3. Các chỉ dẫn 3.3.3. Các chỉ dẫn Chỉ dẫn DB (Define Byte) Chỉ dẫn DW (Define word) • Chỉ dẫn này tương tự DB nhưng mỗi phần tử được gán Địa chỉ Mô tả Bit cho một vùng nhớ 2 byte (word) 500h 12h 501h 55h [Label:] DW Expression 502h 64h Ví dụ: ORG 600h 503h 08h DATA: DW 1234h, 515h, 64h, …. 504h …., …, …., ⇒ Định nghĩa DATA gồm các giá trị: 12h, 55h, 64h, ….nằm trong bộ nhớ ROM với địa chỉ bắt đầu 600h 3.3.3. Các chỉ dẫn Nội dung: Chỉ dẫn DW (Define word) • Chương 1: Giới thiệu về Vi xử lý Địa chỉ Mô tả Bit • Chương 2: Giới thiệu về cấu trúc của Họ Vi điều 600h 34h khiển 8051 601h 12h • Chương 3: Khảo sát tập lệnh và lập trình Vi điều 602h 15h khiển 8051 603h 05h • Chương 4: Hoạt động của bộ định thời 604h 64h • Chương 5: Hoạt động ngắt 605h 00 • Chương 6: Hoạt động truyền thông nối tiếp 606h …., • Chương 7: Thiết kế giao tiếp …, ….,