Ch01

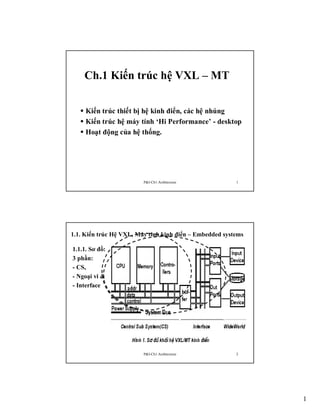

- 1. Ch.1 Kiến trúc hệ VXL – MT Kiến trúc thiết bị hệ kinh điển, các hệ nhúng Kiến trúc hệ máy tính ‘Hi Performance’ - desktop Hoạt động của hệ thống. P&I-Ch1:Architecture 1 1.1. Kiến trúc Hệ VXL, Máy tính kinh điển – Embedded systems 1.1.1. Sơ đồ: 3 phần: - CS, - Ngoại vi & - Interface P&I-Ch1:Architecture 2 1

- 2. 1.1.1. a. Central Sub System – CS: + CPU: Central Processing Unit: • Khái niệm: Là bộ điều khiển trung tâm, thực hiện công việc được giao đặt trong bộ nhớ chương trình bằng cách thực hiện các phép xử lý lên các biến nhị phân và điều khiển thiết bị ngoại vi. • Công việc bao gồm: – Tìm lệnh, giải mã lệnh, [tìm toán hạng, xử lý và cất kết quả], – In/Out với các port kiểu Interrupt và DMA để điều khiển thiết bị ngoại vi. P&I-Ch1:Architecture 3 Đặc trưng – Specifications: • Kích thước toán hạng (bit): 4, 8, 12, 16, 32, 64... • Tốc độ xử lý: Mips/Gips, clock multiplier, • Kiến trúc: – RISC (Reduced Instruction Set Computer)vs CISC (Complex Instruction Set Computer), – DSP – Digital Signal Processor, – Micro Controller (Micro Computer One Chip - All in one): • Atmel: ATmega nnn (8bit, RISC), AT91SAMnnn (ARM core) • MicroChip, PICxxx • Cypress: PSoC... • Pinning/Signalling (Data/Address - Mux, Control bus, IRQ, HRQ, RD/WR...), • Register set, • Instruction set – Addressing Modes, • Power Modes: Slow/ sleep/ power down modes, Mips/Wattage • ... P&I-Ch1:Architecture 4 2

- 3. + Memories (Semiconductor): K/n & ROM: Khái niệm: • Lưu thông tin (ch/tr và số liệu) dạng nhị phân, • Dung lượng lớn (upto 100s Mega bit), tốc độ truy nhập nhanh (downto ns access time). – Physically: tính chất vật lý như thế nào? • ROMs: Mask ROM, PROM, EPROM, EAROM, OTROM, NonVolatile mem, ... • Là bộ nhớ chỉ đọc, vẫn lưu thông tin khi mất điện, • Package : byte • Access time:100..120ns • Ghi/nạp nội dung: T/bị chuyên dùng (ROM Burner /Programmator) • Shadow ROM?: copy nội dung từ ROM sang DRAM mỗi khi khởi P&I-Ch1:Architecture 5 động Memories (Semiconductor): SRAM Lưu thông tin tạm thời, không lưu được khi mất điện, đọc và ghi được, [Read/Write Mem], - Static RAM: nhanh (80..3 ns), byte/nibble package, mật độ byte/chip nhỏ (upto 64/256 KB/ chip), đắt, tiêu thụ công suất nhiều, - CMOS RAM: chậm và tiêu thụ cực ít, less W. Vdụ: MC 146818 RealTimeClock-CMOS RAM • Dùng trong các hệ nhỏ, cache memory. • P&I-Ch1:Architecture 6 3

- 4. Memories (Semiconductor): DRAM Dynamic RAM - DRAM: Tốc độ/Access time (50-70ns), [10..20ns] Pre-fetched Mật độ: bit/chip >> (1 Gbit/chip – 1996, Korea), bit package => DRAM bank, Tiêu thụ W, công suất nhỏ. Thông tin chỉ lưu được 10ms => refreshing DRAM với chu ký @ 7,5ms => phức tạp. Dùng trong các hệ có dung lượng nhớ lớn: desktop, laptop, server… P&I-Ch1:Architecture 7 Memories (Semiconductor): FLASH & Others Flash memory: - EAROM typed, đọc được, xoá từng bank, ghi lại được từng byte. - Thông tin lưu được 20 năm, dùng nhiều hiện tại và tương lai: BIOS, diskchip, USB stick Mem, uC... - Serial EAROM/FLASH: dùng để lưu configuration, dùng bus I2C (Philips). Ví dụ ứng dụng : thẻ vi mạch, TV, ... Dual [Quad] Ported RAM: Switching Sys., PGA • RAM-DAC: VGA, VoiceChip • PCMCIA • .... P&I-Ch1:Architecture 8 4

- 5. Memories (Semiconductor): Logically: Bộ nhớ chưa thông tin gì? Program memory: Chứa ch/tr đang thực hiện Data memory: Các biến ngẫu nhiên, các biến có cấu trúc, các số liệu có kiểu truy nhập đặc biệt (FIFO, LIFO…) P&I-Ch1:Architecture 9 Controllers: [Optional], vi mạch, nâng hiệu nang (performance) hệ thống, bao gồm: + - Bộ điều khiển ưu tiên ngắt PIC – Priority Interrupt Controller, Intel 8259A - Bộ điều khiển truy nhập trực tiếp bộ nhớ DMAC – Direct memory Access Controller, Intel 8237A. - Timer: mạch tạo các khoảng thời gian, PITProgrammable Interval Timer, Intel 8254. - Mạch quản trị nhớ: MMU- Memory Management Unit, sau này, thường được built on chip với CPU. Bus controller/Arbitor P&I-Ch1:Architecture 10 5

- 6. System Bus: K/n • PCB (Printed Circuit Board)/ Cable (Twisted pairs, flat..), slot, connector... dùng để chuyển thong tin và năng lượng. • Nối hơn 1 slave/master device, time sharing (dùng chung) • Thông tin: Address, data, control, status, Power Supply • Chiều (dir), 3 state (Hi Z), Loading • ADDRESS BUS: – Từ các BusMaster (CPU, DMAC, PCI host Controller) đến SlaveDevices (Mem, Ports) để chọn/ chỏ từng IO/ Mem location trong từng chu kỳ bus – n Addr bit 2n Mem Locations & 2m IO Locations, m<n. Các CPU 32bit, Addr và Data sharing - multiplexed P&I-Ch1:Architecture 11 System Bus : Data bus DATA BUS: Số bit (thường) phù hợp với kích thước ALU (8/16/32/64 bit) Chuyển Op-code (mã lệnh) trong chu kỳ máy M1, - CPU <= Program Memory, trong các bus cycle M1 Vận chuyển data: - CPU <=> Data memory, - CPU <=> IO Ports và - Data Memory <=> IO Ports, DMA P&I-Ch1:Architecture 12 6

- 7. System Bus : CONTROL/STATUS BUS: gồm các tín hiệu – control bus: Control/ Response: CPU to Others (MEMR, MEMW, IOR, IOW, INTA, HLDA, BHE...), from CPU Status/Request to CPU: IRQ, HRQ, Ready, ... to CPU P&I-Ch1:Architecture 13 System Bus: Power Supply: +5V 5%, 10 đến 20 Amp, cấp cho các Vi mạch số, RedWire. (3.3V and less) Ground, Gnd, 0V, signal reference ground, chassis, BlackWire. +12V 10%, 1Amp, cấp cho các mạch analog, motors, RS232, YellowWire. -12V 10%, 1Amp, (như trên), BlueWire. - 5 V5%, 0.5 Amp, analog circuitries, WhiteWire. Power good: OrangeWire - MicroControlled Power Supply P&I-Ch1:Architecture 14 7

- 8. 1.1.1.B. THIẾT BỊ NGOẠI VI: Input, Output và dada Storage devices Data Input Devices: - Key board/ Key pad, Touch SCR: số phím, công nghệ phím, kiểu dò phím, output code, ghép nối CS - Mouse, track ball - Scanner, Camera, Camcoder Optical Mouse, BarCode reader: Colors, resolution, f, công nghệ CCD - Charge Couple Device, graphics file bit map - bmp. - Digitizer, nhập graphics file vector - bản đồ - Light Pen, Joy stick (Games) - Demodulator (MODEM): Giải điều chế Kiểu điều chế, tốc độ bps, kiểu nén - Microphone, - Reader: RFID Radio Frequency Identification, Finger print - Laser/ LED - Sensor, Transducers, Transmitters: Vật liệu, thiết bị,.. biến đổi các đại lượng vật lý - không điện, thành tin shiệu điện độ nhậy, độ tuyến P&I-Ch1:Architecture 15 tính, dải đo... 1.1.1.B. T/BỊ NGOẠI VI: Data Output Devices: - Displays: Kiểu hiển thị: Point/ 7Seg/ Text/ Graphics; Mono Chrome/Color (color numbers); Size, indoor/outdoor, Resolution, Rate of Refreshing... - Công nghệ: - LED (Light Emitting Diodes): point, 7(16), Segment, Matrix character box (Bill Board), - Outdoor LED Screen... - Organic LED, - LCD (Liquid Crystal Display): single color, color, active, TFT (thin film transistor - CRT (Cathode Ray Tube). P&I-Ch1:Architecture 16 8

- 9. 1.1.1.B. T/BỊ NGOẠI VI: Data Output Devices: PRINTERS: Spec: Text-Graphics, Mono-Color, Resolution, ppm – page per minute, Size, Line-PostScript, media... : Pin Printer, Jet Printer, Laser Printer, Thermal Transfer Printer, barcode Printer. High Speed Text Printer, ... P&I-Ch1:Architecture 17 1.1.1.B. T/BỊ NGOẠI VI: Data Output Devices: Others - Plotter, jet Modulator (MODEM) – điều chế Speaker Actuator: Motor (dc/ac, Step), Relay, Valve, P&I-Ch1:Architecture 18 9

- 10. 1.1.1.b. T/bị Ngoại vi: Massive Storages: - Magnetic devices: FDD, HDD, RAID, Tape backup drive... - Optical devices: CD [Writer] Drives, Magnetic Optic disk drive... - Semiconductor devices: FlashChip, PCMCIA Card... - Tốc độ truy nhập và dung lượng lớn P&I-Ch1:Architecture 19 1.1.1.c. Interface: • Lý do cần interface: khác nhau giưa CS và wide world: – Mức tín hiệu (dòng, áp, analog ... ), kiểu biểu diễn tin tức (nhiệt độ, áp suất, level... bit) – Tốc độ làm việc/tốc độ trao đổi số liệu, – Không đồng bộ... – Nên cần có mạch điện tử để thích ứng (Adapting - ports) và ch/tr điều khiển, gồm: – Thiết bị (Hardware Circuitries - Adaptors): cổng IO: • Input/Output Ports: (Parallel/Serial): ghep nối với Computerized devices PPP (KB, Printer, Mouse, Scanner, Modem, camera,... dùng VXL đa nang), character typed devices • Controllers: thực chất là nhưng hệ VXL chuyên dùng - để ghép nối với nhung thiết bị chuyên dùng FDC, HDC (IDE, EIDE), CRTC (EGA, VGA, SVGA...), block typed devices • Converter: để chuyển đổi tín hiệu số thành tương tự và ngược lại: ADC, DAC, ví dụ sound card, CMOS sensor... P&I-Ch1:Architecture 20 10

- 11. IO buses: • Expansion bus, IO bus, IO system, ... • ISA, EISA, MC, PCI, USB, IEEE 1394, SSA, IEEE 488, SATA ... P&I-Ch1:Architecture 21 1.1.1.C. INTERFACE: Ch/tr điều khiển – Device Driver: - K/n: Hardware or Software? + Software: sản phẩm của NN lập trinh + Hardware: luôn gan liền với IO hardware Liên kết System Programs and/or Application Programs với IO hardware (SPIs và APIs). Các hàm của thiết bị, BIOS, OS hoặc theo ứng dụng: SLLs, DLLs, DRVs, ... Hiện 1 xâu ký tự: – – – – mov ah,9 mov dx,offset xau int 21h mov ah,0 int 16h ; BIOS same mov ah,1 int 21h P&I-Ch1:Architecture 22 11

- 12. Case study PC layers Fig. 1b: PC’s Layers (IBM PC Institute) a P&I-Ch1:Architecture 23 1.1.2. KIẾN TRÚC MÁY TÍNH HIỆU NĂNG CAO - HI PERFORMANCE ARCHITECTURE (SERVER, DESKTOP, LAPTOP) P&I-Ch1:Architecture 24 12

- 13. 1.1.2. HI-PER. ARCHITECTURE:1.1.2.a. Local Buses: Ví dụ VESA VL-Bus 2.0 [late 1993], Memory [1985]. Also called system/host/processor bus. Chỉ liên kết CPU, MMU (gồm Cache, DRAM, shadowed ROM ) và PCI Host [Bridge], ít, gần, unbuffered (direct connected to Processor); 33, 66, 100, 133, 200, 400, 800 MHz... clock. 32 bit A/D (16 bit support also), burst mode, max 132 MBps, Addr D0 D1 D2 (data 4 byte) D3 D4 H.1.3. Ví dụ burst mode: P&I-Ch1:Architecture 25 1.1.2. HI-PER ARCHITECTURE:1.1.2.b. Hi Speed Bus: Peripheral Component Interconnect - PCI - 5/1993, Intel Ver. 2.0, Open Standard, - Local bus, mức trung gian giữa Local và các bus chuẩn khác (ISA, MC, EISA) thông qua PIC Bridge/Controller. - Có kiểm tra parity cho Addr và Data - Auto configuration of all PCI devices, share the same IRQ. - Disabling IRQ => cấm toàn bộ PCI devices. - No DMA, device on PCI bus là bus master (Tốt cho việc dùng MultiTasking OS). - Burst mode: 32 bit @33MHz --> 96..132MBps, tuỳ thuộc số byte (từ 32 byte đến 4KB). Option 64bit @33MHz --> 264MBps - Most Platforms use:Intel, DEC Alpha, PowerPC, Spark - Modern OS: ‘Block Typed Devices’: tần suất vận chuyển cao, nhanh, data block P&I-Ch1:Architecture 26 13

- 14. 1.1.2. HI-PER ARCHITECTURE:1.1.2.c. Expansion Bus: - So called: standard buses, expansion bus, slots, IO bus, IO system, channel bus): ISA, EISA, MC... - MC bus: 32 bit, 10MHz, 20..40MBps, 15 BusMaster, Auto config, 1987, IBM - EISA bus: 32 bit, 8,33 MHz, 33MBps, 4 BMs, AutoConfig (EISA card only), 1989, Compaq - ISA (Industry Small Architecture), AT bus: - Spec. 8/16 bit (data), 8MHz..11MHz, 5..5 MBps max, 1 Bus Master, no PnP, 1984, IBM. - Rất phổ biến, còn tồn tại lâu, Espec. @ iPC, - Hạn chế số IRQs, 4 DRQs, - Dùng DIP switch/jumper để config. - No data integrity features (no party checking) - Modern OS: ‘Character Typed Devices’ P&I-Ch1:Architecture 27 1.2. HOẠT ĐỘNG CỦA HỆ THỐNG: Reset, Opcode fetch and Execute, Interrupt, DMA - halt & Ready (wait state - ws) P&I-Ch1:Architecture 28 14

- 15. 1.2. HOẠT ĐỘNG:1.2.1. Lưu đồ tổng quát: reset ProgCounter = ResetAddr/vector DMA? n y IRQ? Machine On Halt y y n y OpCode Fetch DMA? n y MaskOn n PC = Intr. Vector OpCodeDecode Execute Hình 1.3. Lưu đồ tổng quát của VXL (Motorola), Training courses P&I-Ch1:Architecture 29 1.2. HOẠT ĐỘNG: 1.2.2. Reset : Cold Start: Bấm nút reset/Power-On =>Xoá trạng thái hiện hành, cấm ngắt, DMA. CPU được khởi tạo (PC-Program Counter (hoặc CS:IP), Flags và SP...). Các thiết bị trong hệ cùng được reset. (Sau khi reset, CPU sẽ tim và t/h lệnh – với các thủ tục sau) Warm Start: do lệnh gọi, (Int 19h, Ctrl_Alt_Del) POST (Power On Self Test - ch/tr monitor/ BIOS) để kiểm tra mọi thiết bị theo nguyên tắc ghi và đọc lại (Registers, RAM) hoặc đọc và kiểm tra Check Sum (ROM). Initializing - khởi tạo: đặt các tham số => configuring. [Máy tính - Nạp hệ điều hành ]. P&I-Ch1:Architecture 30 15

- 16. 1.2.3. DMA: (Xem Ch. 3.2.) 1.2.4. Interrupt: (Xem Ch. 3.3.) P&I-Ch1:Architecture 31 1.2. HOẠT ĐỘNG: 1.2.5. Tìm và thực hiện lệnh : - Diễn ra chủ yếu trong thời gian hoạt động, ngoại trừ lệnh HLT. - Ch/tr ngôn ngữ máy: tập hợp các lệnh có cấu trúc, có nghĩa, thực hiện 1 thuật toán. - Chu kỳ lệnh (Instruction Cycle): Khoảng thời gian CPU thực hiện xong 1 lệnh, gồm: tìm lệnh, giải mã lệnh, [tìm toán hạng và thực hiện lệnh (thực hiện các phép xử lý hoặc vào-ra)]. ộ dài lệnh: (CISC)1 hay nhiều byte, Thời gian t/h:(CISC)1/nhiều chu kỳ máy (chu kỳ bus). Chu kỳ máy (Bus/Machine Cycle): thời gian BusMaster thực hiện thao tác trên bus: đọc/ghi ô nhớ hay IO port Clock cycle: Chu kỳ máy: 4..12 chu kỳ clock, tuỳ CPU. P&I-Ch1:Architecture 32 16

- 17. 1.2. HOẠT ĐỘNG: 1.2.5. Tìm và thực hiện lệnh : - Diễn ra chủ yếu trong thời gian hoạt động, ngoại trừ lệnh HLT. - Ch/tr ngôn ngữ máy: tập hợp các lệnh có cấu trúc, có nghĩa, thực hiện 1 thuật toán. - Chu kỳ lệnh (Instruction Cycle): Khoảng thời gian CPU thực hiện xong 1 lệnh, gồm: tìm lệnh, giải mã lệnh, [tìm toán hạng và thực hiện lệnh (thực hiện các phép xử lý hoặc vào-ra)]. ộ dài lệnh: (CISC)1 hay nhiều byte, Thời gian t/h:(CISC)1/nhiều chu kỳ máy (chu kỳ bus). Chu kỳ máy (Bus/Machine Cycle): thời gian BusMaster thực hiện thao tác trên bus: đọc/ghi ô nhớ hay IO port Clock cycle: Chu kỳ máy: 4..12 chu kỳ clock, tuỳ CPU. P&I-Ch1:Architecture 33 1.2. HOẠT ĐỘNG: 1.2.5. Tìm và thực hiện lệnh : - Diễn ra chủ yếu trong thời gian hoạt động, ngoại trừ lệnh HLT. - Ch/tr ngôn ngữ máy: tập hợp các lệnh có cấu trúc, có nghĩa, thực hiện 1 thuật toán. - Chu kỳ lệnh (Instruction Cycle): Khoảng thời gian CPU thực hiện xong 1 lệnh, gồm: tìm lệnh, giải mã lệnh, [tìm toán hạng và thực hiện lệnh (thực hiện các phép xử lý hoặc vào-ra)]. Độ dài lệnh: (CISC)1 hay nhiều byte, Thời gian t/h:(CISC)1/nhiều chu kỳ máy (chu kỳ bus). Chu kỳ máy (Bus/Machine Cycle): thời gian BusMaster thực hiện thao tác trên bus: đọc/ghi ô nhớ hay IO port Clock cycle: Chu kỳ máy: 4..12 chu kỳ clock, tuỳ CPU. P&I-Ch1:Architecture 34 17

- 18. 1.2. HOẠT ĐỘNG: 8 CPU’s + DMA Bus cycles: - M1, opcode fetching, Addr =>Program mem, -MEMR - Data mem Reading, Addr=>Data mem, -MEMR - Data mem Writing, Addr=>Data mem, -MEMW - Input Port Reading, Addr=> IO space, -IOR - Out Port Writing, Addr => IO space, -IOW - Interrupt Acknowledge, -INTA, - Halt, waiting for Ext. Intr. hoặc reset - Bus Idle Thêm 2 chu kỳ bus của DMAC: - IOR-MemW DMA bus cycle và - MemR-IOW DMA bus cycle. P&I-Ch1:Architecture 35 1.2. HOẠT ĐỘNG: 1.2.6. Wait State (Ready): - Thường dùng để ghép nối: bộ nhớ, ngoại vi tốc độ chậm. - Hoạt động Khi BusMaster phát địa chỉ & tín hiệu đọc/ghi (thêm các tín hiệu khác) để thực hiện 1 chu kỳ bus, MMU/IO port [Controller] chủ động phát ra tín hiệu Ready=0 (not Ready) để yêu cầu BusMaster giữ nguyên trạng thái bus thêm 1 [vài] nhịp clock. P&I-Ch1:Architecture 36 18

- 19. Case Study: IOW bus cycles w/o and w 1 wait state: P&I-Ch1:Architecture 37 1.3. Thiết bị ngoại vi: 1.3.1. Key boards: • Khái niệm: – Thiết bị nhập số liệu và ra lệnh cho máy – Phân loại theo công nghệ: • Contact keys • Non contact keys: Cap/Ind – ít dùng • Membrane keys: contact key – Technical Problems: • Key bouncing: • key debouced Tech – RS FF (cổ), delay • Ghost keys: Nhiều phím bấm đồng thời – Bàn phiams được tổ chức thành ma trận nxm. – Giải pháp: không đọc, đọc bấm trước/nhả sau P&I-Ch1:Architecture 38 19

- 20. • Key organization: matrix • Key polling: Là KT xác định hàng/cột – Line reversal technique: (Fig. 1.5) – Scan (Fig.) P&I-Ch1:Architecture 39 P&I-Ch1:Architecture 40 20

- 23. Scan procedure (Fig 904a) • PC keyboard: 15 col – 8 row 1. i=0 2. Col (i) =0 only, delay(1) 3. If Rows <> 1111 1111 then (5) 4. Inc (i), if i>15 then goto (1) 5. Delay for debouncing. Read Row code, Read Col code, encode Col-Row. 6. Convert R-C => KB Scanned code 7. Sending to PC bit by bit. 8. Polling for key releasing and delay for debouncing 9. Goto (2) P&I-Ch1:Architecture 45 P&I-Ch1:Architecture 46 23

- 25. Bài tập chương 1 • Tìm hiểu bus ISA (Ch4), thiết kế mạch logic để chèn các ws cho ISA slot khi CPU đọc/ ghi 1 địa chỉ cổng • Tạo mạch kiểm tra parity - 74HC280 P&I-Ch1:Architecture 49 25